#### 応用物理学会

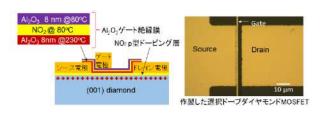

薄膜・表面物理分科会/シリコンテクノロジー分科会共催特別研究会

# 第29回 電子デバイス界面テクノロジー研究会 ――材料・プロセス・デバイス特性の物理―

日時 2024年1月31日(水)~2月2日(金)

場所 東レ総合研修センター

協賛: 日本物理学会、日本化学会、日本金属学会、日本表面真空学会、

電子情報通信学会、電気学会、触媒学会、電気化学会、 表面技術協会、日本顕微鏡学会、日本セラミックス協会、

精密工学会

開催助成: 静岡県東部地域コンベンションビューロー

協賛企業: 株式会社アクシス、株式会社アールデック、

株式会社 KOKUSAI ELECTRIC、株式会社コメット、 シエンタオミクロン株式会社、株式会社スプリード、

東京エレクトロン株式会社、株式会社東レリサーチセンター

### 卓上型液体窒素プローバーシステム

**AX-LPS-TS02**

### ≪システム構成≫

液体窒素クライオスタット 真空チャンバー 温度センサー、温調用ヒーター マニピュレーター4式

CCDカメラ、液晶モニター

### ≪システム仕様≫

液体窒素量 : 約1L

温調範囲: 80K~500K

試料サイズ : □20mm

移 動 量 : X.Y18mm, Z10mm

サ イ ズ : □480mm,H428mm

### 100V空冷式圧縮機使用 小型無冷媒マグネット

☆同軸変換/気密コネクタ ☆回転ホルダー その他

株式会社アクシス

〒305-0043 茨城県つくば市大角豆646-2 TEL:029-849-2220 FAX:029-849-2221

Mai I: info@axj.co.jp URL: https://axis.company

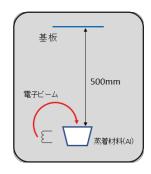

### 成膜レシピ制御型自動蒸着装置 ADS-E86

- ・独自開発ソフトで、基板セット後は"ワンクリック"するだけ。

- 全自動で多層膜蒸着を行える研究開発用の蒸着装置。

- ・どなたにでも安全で簡単に操作可能。

### 特徵

- ・高融点金属から半導体、酸化物まで蒸着が可能

- 多層膜連続成膜制御

- ・高性能 6 連電子ビーム蒸着源

- ・リフトオフ蒸着に最適な基板冷却機構を装備

- ・成膜条件を選択して『START』ボタンをクリックするだけで、 真空排気から成膜完了まで自動制御

- ・基板サイズ□10 mm ~ φ8 インチ

- ・ 高速真空排気 (L/L 室: 大気圧から E-3 Pa まで 3 分以内)

### アルミ蒸着試験参考データ(試験①)-

| バッチNo | 膜厚(nm)-50mm | 膜厚(nm)+50mm |

|-------|-------------|-------------|

| 1     | 594.6       | 594.1       |

| 2     | 596.2       | 597         |

| 3     | 589.5       | 591.7       |

| 4     | 597.5       | 598.8       |

| ⑤     | 601.8       | 600.9       |

| 6     | 595.6       | 597.7       |

| 7     | 594.9       | 597.8       |

| 8     | 599.8       | 603.4       |

| 9     | 600.8       | 598.7       |

| 10    | 591.5       | 595.3       |

データ提供:日本電子株式会社 様

### 高感度昇温脱離ガス分析装置 HTDS-004 SEMI

- ・超高真空下でサンプルを加熱昇温する際に脱離されるガスをリアルタイム測定し定性・定量分析。

- ・半導体ウェハ、PCB 基板、電子部品からの脱離ガスを wt・ppm で分析可能。

#### 特徵

- ・試料サイズ:最大φ10×30mm→大きな実試料も測定可能

- ・測定範囲:質量数 200 amu → CxHv 成分も測定可能

- ·加熱温度:室温 ~ 1000℃

- ・分析室にタンデムターボポンプ採用 → 到達圧力: <5.0E-8Pa

高感度リアルタイム分析

- ・定量ソフトで wt•ppm が簡単に計算可能

- ・水素標準リークシステム内蔵 → 長期間安定した測定が可能

社 〒305-0051 茨城県つくば市二の宮1丁目16番10号

TEL **029-858-0211** FAX029-855-9877

〒113-0033 東京都文京区本郷3丁目15番4号 本郷小林ビル5F

TEL 03-5805-0330 FAX03-5805-0331

# 技術と対話で未来をつくる

誰も想像がつかないような革新をもたらし続ける半導体。

私たちは、進化する半導体の最先端を担う半導体製造装置専業メーカーとして 事業活動とESGの取り組み\*の両側面からサステナビリティ経営に取り組んでいます。

※環境・社会課題の解決、ガバナンスの強化

TSURUGI-C<sup>2®</sup>剱<sup>®</sup> 高品質成膜·高性能半導体製造装置

MARORA®

枚葉プラズマ窒化・酸化装置

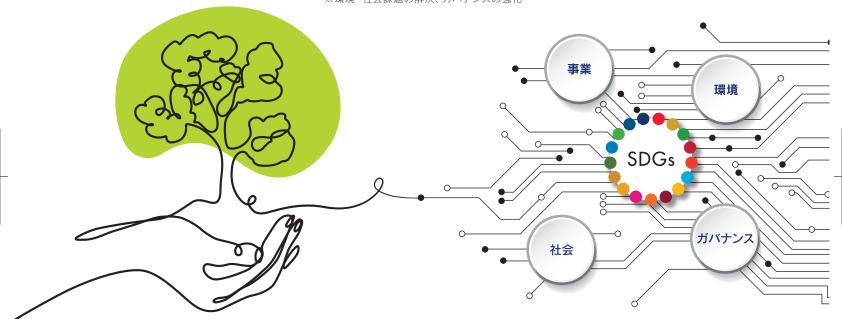

## 最適材料探索を一気に加速 コンビナトリアル・テクノロジー

- ◇ コンビナトリアル材料合成手法を使った新規機能性材料の受託開発

- ◇ コンビナトリアル特性解析: 各種の多点物理分析を致します

- ◇ コンビナトリアル材料合成装置の販売

NEW!

・コンビナトリアルスパッタ装置 CMS-6420, CMS-3200 6420: Max 6元 x 4" ウェハ対応, 3200: Max 3元 x 2" ウェハ対応

4インチウェハ上に形成した3 元組成傾斜膜 (ZnO-TiO<sub>2</sub>-WO<sub>3</sub>)

(ZnO-TiO<sub>2</sub>2元系)

CMS-6420. 3200の特徴

- 2元 & 3元コンビ成膜に対応

- PCからのレシピ入力 & 自動成膜に対応

- タッチパネルで簡単操作(自動排気、成膜プロセス)

- 基板加熱可能(標準仕様:最高650℃)

- ロードロック室での高温アニール可能(オプション)

### 経験豊かな技術スタッフが材料開発をお手伝いします

株式会社コメット

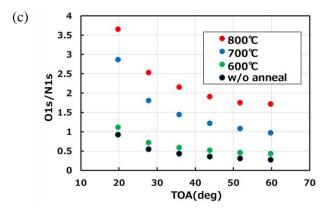

ntensity (arb. units)

https://www.comet-nht.com

〒300-2635 茨城県つくば市東光台5丁目9番5号

Phone: 029-869-8620, Fax: 029-869-8621, E-mail: inquiries@comet-nht.com

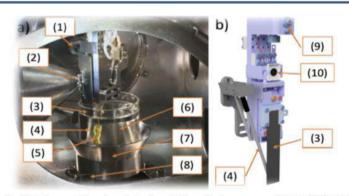

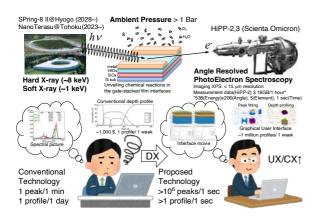

# **Ambient Pressure Photoelectron Spectroscopy**

### **HiPP Lab**

Advanced Measurements Made Easy

- •Measure XPS with **several mbar pressure** at the sample

- •Robust, flexible and easy to use system ensuring speed to result

- · Easy to extend functionality with other modules and with the material innovation platform

For Studies of Industrially Relevant Catalytic Reactions

- Study of catalytic reactions

- •Measuring XPS under conditions of > 1 bar of pressure

- •Open-up the possibility of operando studies of heterogeneous catalytic reactions under industrial manufacturing conditions

#### Hipp-lab with glove box

Customer installation example

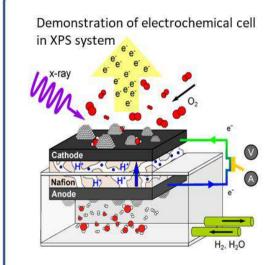

### Electrochemical XPS (Dip & Pull method)

Swiss Light Source: Zbynek et al. Review of Scientific Instruments, 91, 023103 (2020) Advanced Light Source: Axnanda, Sci rep 5(2015) 09788 MAX IV Laboratory: Zhu et al Journal of Synchrotron Radiation (2021), 28, 624-636

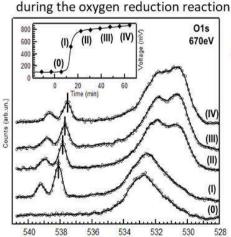

### Application of Electrochemical Cell

H. S. Casalongue et al. Nature Comm. 4, 2817 (2013)

Probing oxygenated species

Binding Energy (eV)

3 electrode system

### 私たちが創るのは研究の新しい扉を開く鍵です

新構造•新材料

# **SPLEAD Atomic Layer Deposition Systems**

AI 時代に向けたプロセス 新たなチャレンジが始まっています

A L D は 近 年 各 種 ア プ リ ケ ー シ ョ ン へ の 応 用 が 飛 躍 的 に 増 加 半導体、化合物半導体デバイスの他、MEMS/NEMS (micro/nanoelectromechanical systems) 光学薄膜、レーザー薄膜、コーティング、腐食防止、2次電池、太陽電池などに代表される再生可能エネルギー 医療機器、生体材料、湿気防止バリアー、ガラスのクラック防止保護膜など、様々な分野に広がりを見せています TMA B(CH3)3 CH3SiC13 TDMAA Ru(EtCp)2 BEMAS MgCp2 TBA Li(t-OBu) POC13 DEZ など

MA B(CH3)3 CH3SICI3 IDMAA RU(ETCP)2 BEMAS MIGCP2 IBA LI(T-OBU) POCI3 DE2 なる 兼 々 な 材 料 の 提 案 が 可 能 で す

### **Analytical Services**

Using latest analytic equipment by experienced skillful technitians

### Contract R&D Support

Backed by cumulated and multidisciplinary expertise

**40+** Year's of experiences in analytical service as your R&D partner

02

01

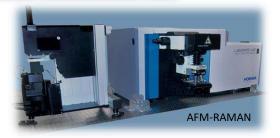

#### ANALYTICAL EQUIPMENT

Cs-corrected TEM/STEM

Dual Beam FIB-SEM

Nano-SIMS 50L , GCIB TOF-SIMS

AFM-RAMAN, AFM-IR

Orbitrap Fusion Lumos

Spiral TOF MALDI/MS

### **TORAY**

Toray Research Center, Inc.

Established in 1978

#### - CONTACT US -

E-mail: bunseki.trc.mb@trc.toray https://www.toray-research.co.jp/en/

| 始時間      | 終了時間    | duration |             | ID       | タイトル                                                                  | 所属                 | 講演者        |

|----------|---------|----------|-------------|----------|-----------------------------------------------------------------------|--------------------|------------|

| 20:00    | 21:30   | 1:30     | チュートリアル     |          | 半導体製造における分析・計測技術の最前線                                                  | 日立製作所              | 人見 敬一郎     |

|          |         |          |             |          |                                                                       |                    |            |

| 024年2月1  |         |          | T           |          |                                                                       |                    |            |

| 開始時間     | 終了時間    |          | 内容          | ID       | タイトル                                                                  | 所属                 | 講演者        |

| 9:00     | 9:10    |          | Opening     |          |                                                                       |                    |            |

| 酸化物半     | 導体・メモリ  |          | Si-MOS界面    |          |                                                                       | ,                  |            |

| 9:10     | 9:40    | 0:30     | 招待講演        |          | 原子層堆積法によるナノシート酸化物半導体トランジスタ                                            | 東京大学               | 小林 正治      |

| 9:40     | 10:00   | 0:20     | 一般講演        | 30       | 原子層堆積法で成膜した非晶質/多結晶In-Ga-Oトランジスタの信頼性                                   | 奈良先端大              | 高橋 崇典      |

| 10:00    | 10:20   | 0:20     | 一般講演        | 12       | 極薄膜AIN酸化で生成したワイドバンドギャップ $Al_2O_3$ 膜によるリーク電流低減実現                       | キオクシア              | 中島 裕亮      |

| 10:20    | 11:10   |          | Break       |          |                                                                       |                    |            |

| 基調講演     | l・ロジックプ | ロセス      |             |          |                                                                       |                    |            |

| 11:10    | 12:00   | 0:50     | 基調講演        |          | Advanced Logic Transistor Process Technology Towards 1-nm Node        | Applied Materials  | 吉田 尚美      |

| 12:00    | 12:10   | 0:10     | 写真撮影        |          |                                                                       |                    |            |

| 12:10    | 13:30   | 1:20     | Lunch       |          |                                                                       |                    |            |

| 3 ポスターセッ | ション     |          |             |          |                                                                       |                    |            |

| 13:30    | 15:00   | 1:30     | ポスターセッショ    | シ        |                                                                       |                    |            |

| 15:00    | 15:30   | 0:30     | Break       |          |                                                                       |                    |            |

| 4 企画セッシ  | ヨン      |          |             |          |                                                                       |                    |            |

| 15:30    | 16:50   | 1:20     | 企画セッション     |          | 2nmノード&Beyondテクノロジーを見据えたロジックデバイスの開発動向                                 |                    |            |

| 16:50    | 17:00   | 0:10     | Break (移動)  |          |                                                                       |                    |            |

| 17:00    | 17:30   | 0:30     | オーサーズ イング   | タビュ      |                                                                       |                    |            |

|          |         |          |             |          |                                                                       |                    |            |

| 懇親会(立:   | 食)      |          |             |          |                                                                       |                    |            |

| 17:30    | 19:30   | 2:00     | 懇親会         |          |                                                                       |                    |            |

|          |         |          |             |          |                                                                       |                    |            |

| 2024年2月2 | !日(金)   |          |             |          |                                                                       |                    |            |

| 開始時間     | 終了時間    |          | 内容          | ID       | タイトル                                                                  | 所属                 | 講演者        |

| 8:45     | 8:50    |          | 2日目案内       |          |                                                                       |                    |            |

| 基調講演     |         |          |             | <u> </u> |                                                                       | L                  |            |

| 8:50     | 9:40    |          | 基調講演        |          | シリコン量子ビットデバイスの特性における界面の影響                                             | 理化学研究所             | 小林 嵩       |

| 9:40     | 10:10   |          | 招待講演        |          | シリコン量子ビット技術と集積化に向けた研究開発                                               | 東京工業大学             | 小寺 哲夫      |

| 10:10    | 10:40   |          | Break       |          | 2 7 2 7 C 7 TAILE A RIOGI TO CONTOURS                                 | SIGNITURE SIGNICIA | 7 5 11/    |

| 5 リザバーコン |         |          |             |          |                                                                       |                    | ļ          |

| 10:40    | 11:10   |          | 招待講演        |          | 金属酸化物およびLi イオンを用いた不揮発素子と脳型リザバーコンピューティング等への応用                          | 東芝                 | 丸亀 孝生      |

| 11:10    | 11:40   |          | 招待講演        |          | 二次元異種材料の接合技術と新機能創出                                                    | 東京大学               | 町田 友樹      |

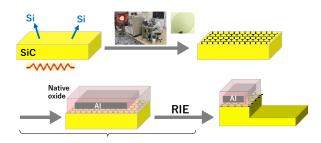

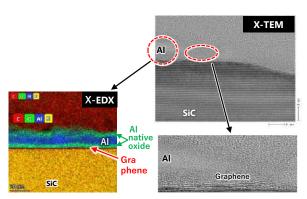

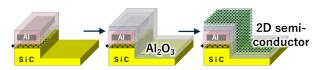

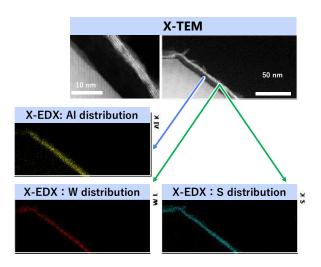

| 11:40    | 12:00   |          | 一般講演        | 21       | 単原子長ゲート構造への二次元半導体結晶の成長                                                | 東北大                | 杉野 秀明      |

| 12:00    | 13:00   |          | Lunch       | 21       | 字形 1 及 7 1 梅廷· W 二次 2 年 4 年 4 日 8 日 8 日 8 日 8 日 8 日 8 日 8 日 8 日 8 日   | 未心人                | 1/21/15/91 |

|          | ·高周波デ/  |          | Lunch       |          |                                                                       |                    |            |

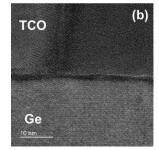

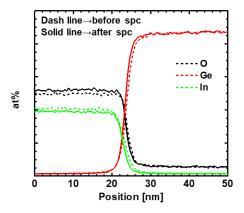

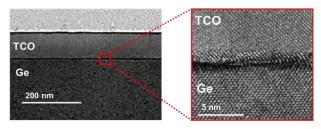

|          | 13:20   |          | 一般講演        | 24       | 1. 0 を活用道面供配化時面標を用いたのショットと フェレグノナ じの成在性研究                             | 東理大                | 石井 寛仁      |

|          |         |          |             |          | In <sub>2</sub> O <sub>3</sub> 系透明導電性酸化膜電極を用いたGeショットキーフォトダイオードの感度特性評価 |                    | 1          |

| 13:20    | 13:40   |          | 一般講演        | _        | Si 基板上 GeSn 細線のレーザー溶融結晶化におけるレーザー走査条件と下地 SiO₂ 膜厚の最適化                   | 阪大                 | 早川雄大       |

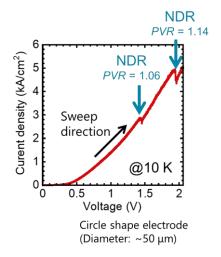

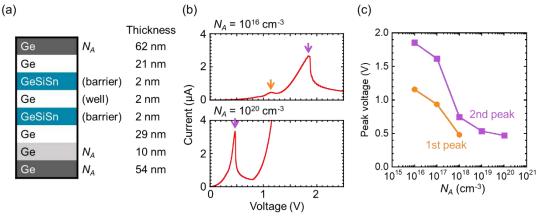

| 13:40    | 14:00   |          | 一般講演        | +        | GeSn/GeSiSn二重障壁構造における負性微分抵抗の発現                                        | 名大                 | 石本 修斗      |

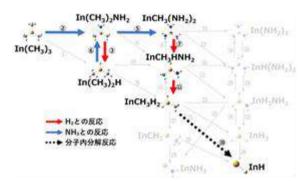

| 14:00    | 14:20   |          | 一般講演        | 17       | InN MOVPE成長過程におけるTMIn分解・反応経路に関する理論研究                                  | 名大                 | 長嶋 佑哉      |

| 14:20    | 14:45   |          | Break       |          |                                                                       |                    |            |

| 3 パワーデバイ | -       |          | I.=         |          |                                                                       | T                  | T          |

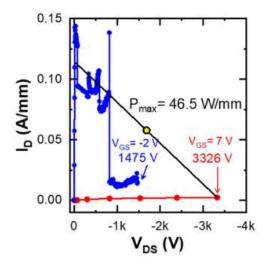

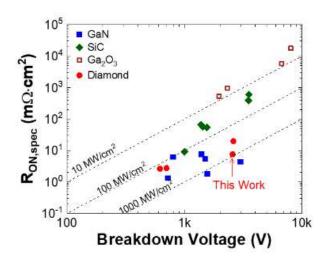

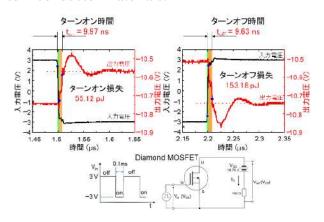

| 14:45    | 15:15   |          | 招待講演        |          | パワー半導体に向けたダイヤモンドMOSFETの最近の進展                                          | 佐賀大学               | 嘉数 誠       |

| 15:15    | 15:35   |          | 一般講演        | +        | GaN/SiO <sub>2</sub> 界面におけるGaOx界面層中のMg <sub>Ga</sub> とVoの相互作用         | 名大                 | 服部 柊人      |

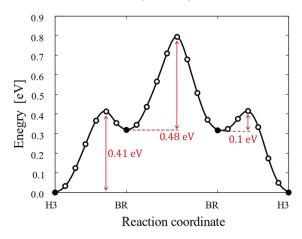

| 15:35    | 15:55   | 0:20     | 一般講演        | 15       | CVD 環境下における SiC(0001)表面への N 原子取り込み機構の理論研究                             | 名大                 | 山内 颯一郎     |

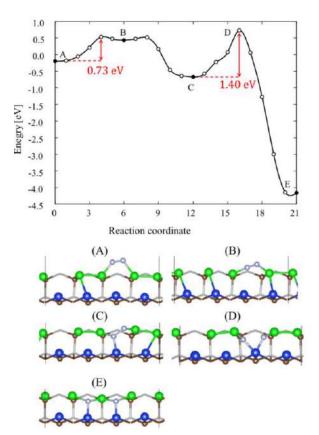

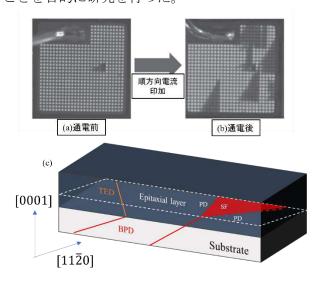

| 15:55    | 16:15   | 0:20     | 一般講演        | 31       | 4H-SiC中における基底面転位(BPD)の第一原理計算を用いた電子構造解析 ~パイポーラ劣化現象の物理的起源の解明~           | 名大                 | 佐野 雅季      |

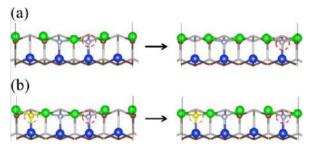

| 16:15    | 16:35   | 0:20     | 一般講演        | 33       | $SiO_2$ ダミープロセスを用いたc及びm面のGaN/Al $_2O_3$ /PtキャパシタのPBS特性の改善             | NIMS               | 生田目 俊秀     |

| 16:35    | 16:45   | 0:10     | Break       |          |                                                                       |                    |            |

| 表彰式・閉会   | :式      |          |             |          |                                                                       |                    |            |

| 16:45    | 17:05   | 0:20     | Closing     |          | 表彰式など                                                                 |                    |            |

| 1        |         |          |             |          |                                                                       |                    |            |

|          |         |          |             |          |                                                                       |                    |            |

| ピスターカッシ  | /ョン:2日1 | 日 (米)    | 13:30-15:00 |          |                                                                       |                    |            |

| ハハノ ピノノ  | コン・L刀「  | H (M)    | Poster      | ır       | タイトル                                                                  | 所属                 | 講演者        |

|          |         |          |             |          |                                                                       | 1//1/(29)          |            |

| N) | 13:30-15:00 |    |                                                      |           |        |

|----|-------------|----|------------------------------------------------------|-----------|--------|

|    | Poster      | ID | タイトル                                                 | 所属        | 講演者    |

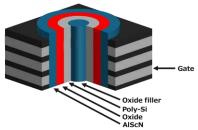

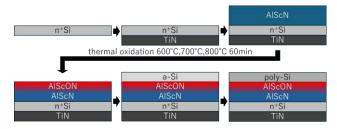

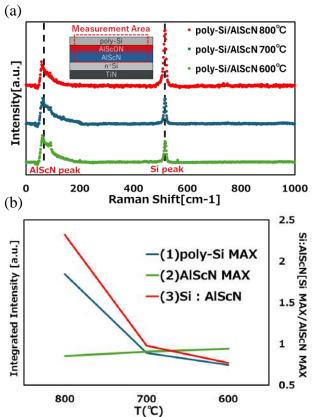

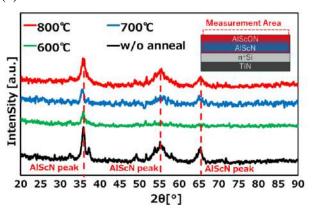

|    | 1           | 20 | C軸配向AlScNを用いた固相成長ポリシリコンチャネルの結晶制御                     | 東京都市大     | 野秋 元   |

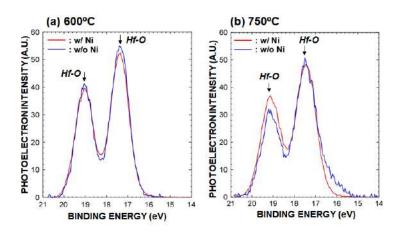

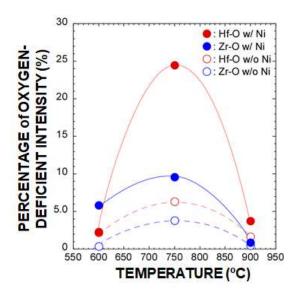

|    | 2           | 24 | HfZr酸化物へのNi電極形成が結晶構造および化学結合状態に与える影響                  | 名大        | 佐野 友之輔 |

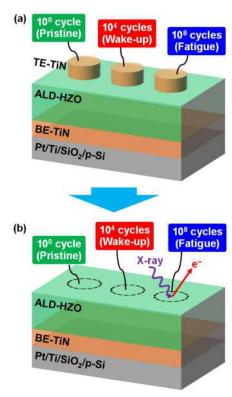

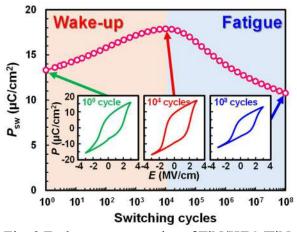

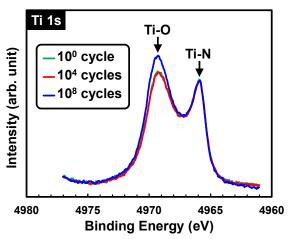

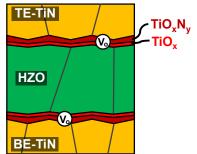

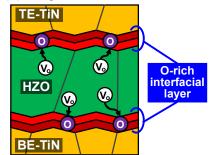

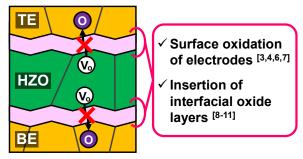

|    | 3           | 46 | 強誘電体HfxZr1-xO2/TiNの界面反応に起因する分極疲労抑制メカニズムに関する考察        | 東大        | 女屋 崇   |

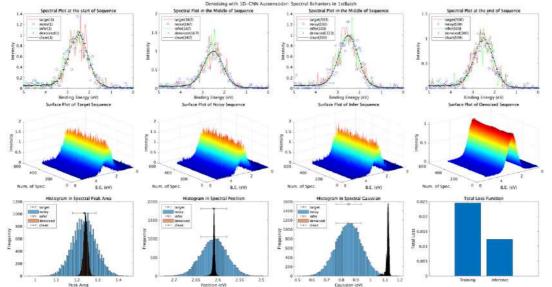

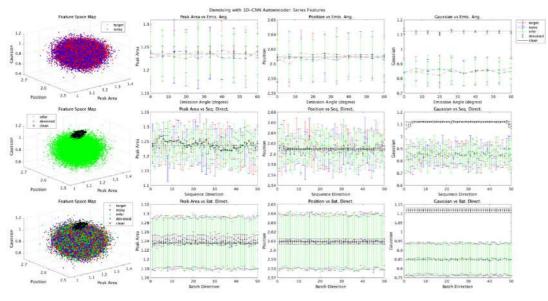

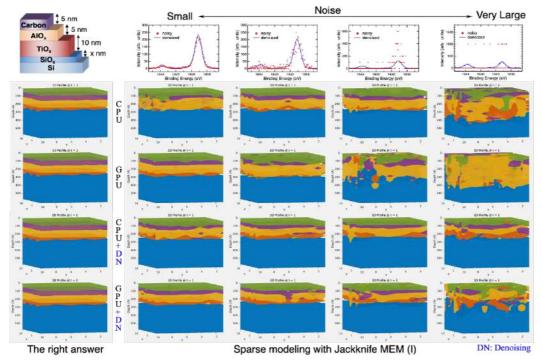

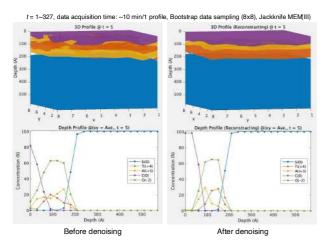

|    | 4           | 43 | XPSスペクトルのNoise2Noiseデノイジングによる多層積層薄膜界面の 高精度時空間深さ方向可視化 | シエンタオミクロン | 豊田 智史  |

|    | 5           | 16 | 角度分解2光子光電子分光法を用いたホールサブバンドの高分解能測定                     | 東レリサーチ    | 坂田 智裕  |

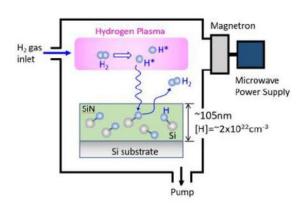

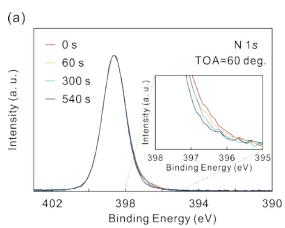

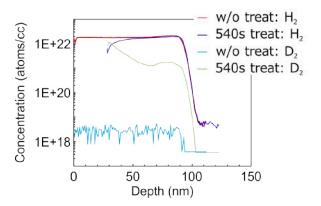

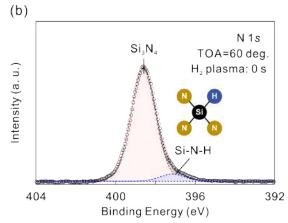

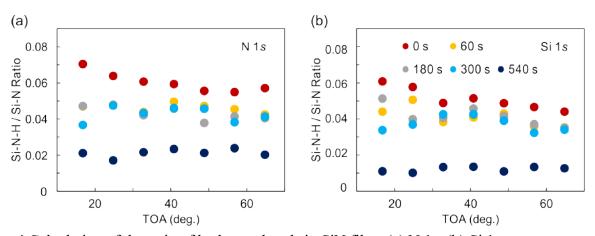

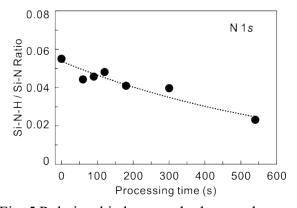

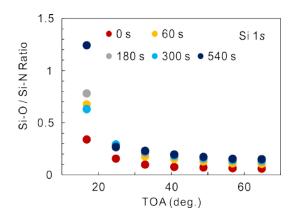

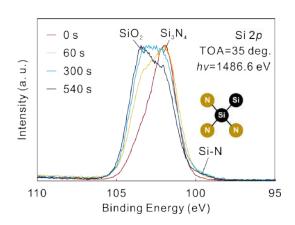

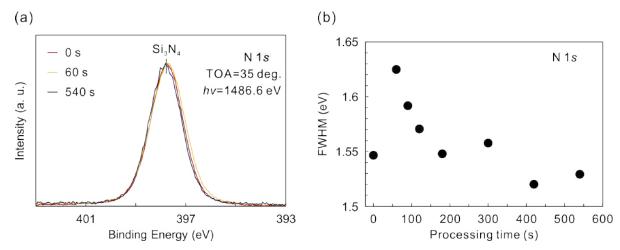

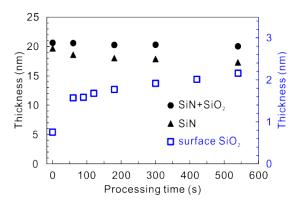

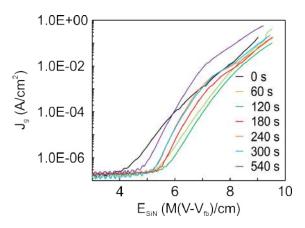

|    | 6           | 40 | SiN膜に含まれる水素の化学結合状態と分布に与える水素プラズマ処理の影響のAR-HAXPES評価     | 東京都市大     | 桐原 芳治  |

| Ī  | 7           | 19 | 水素プラズマ処理によるALD-SiO <sub>2</sub> 膜中トラップエネルギー準位の深化     | 東京都市大     | 藤田 雄輝  |

|    | 8           | 35 | 電子線照射によるSiO <sub>2</sub> /Si界面欠陥生成                   | 筑波大       | 清水 峻央  |

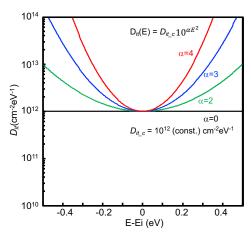

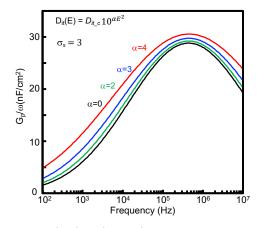

| Ī  | 9           | 22 | MOS構造における界面準位密度分布とコンダクタンスカーブ形状の関係                    | 愛工大       | 田岡 紀之  |

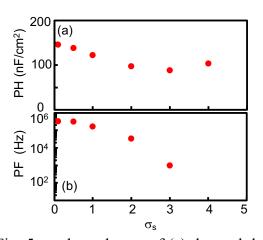

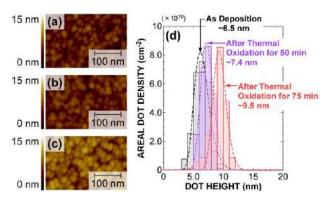

| 10 | 44 | 一次元連結・高密度Si量子ドットの形成と局所帯電特性評価                                                  | 名大    | 今井 友貴 |

|----|----|-------------------------------------------------------------------------------|-------|-------|

| 11 | 45 | 極薄熱酸化SiO <sub>2</sub> 上の自己組織化Si量子ドットの形成機構                                     | 名大    | 白 鍾銀  |

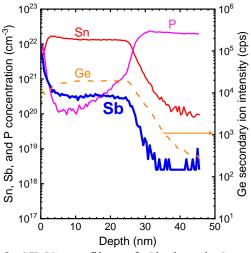

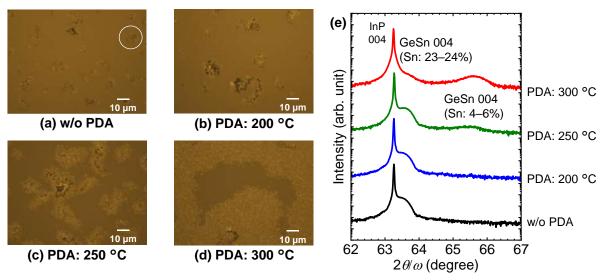

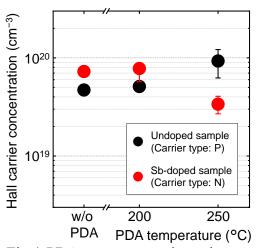

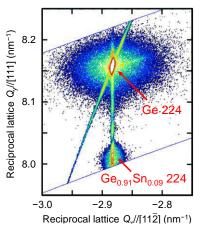

| 12 | 39 | In-situ SbドーピングによるInP上n型Ge <sub>0.75</sub> Sn <sub>0.25</sub> エピタキシャル膜の形成     | 名大    | 柴山 茂久 |

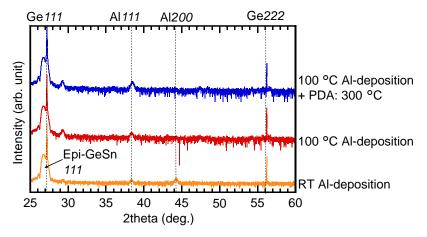

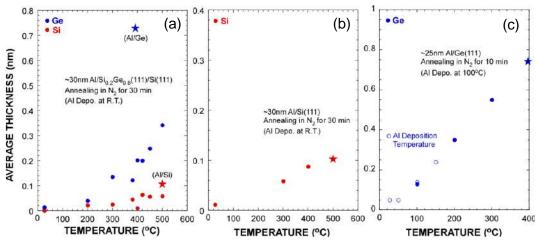

| 13 | 38 | Al/GeSn(111)構造上への熱処理による極薄・高Sn組成GeSn表面偏析                                       | 名大    | 柴山 茂久 |

| 14 | 25 | Al/SiGe(111)/Si(111)構造の化学構造分析 -熱処理による Si および Ge 偏析-                           | 名大    | 酒井 大希 |

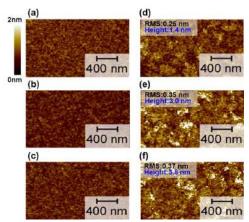

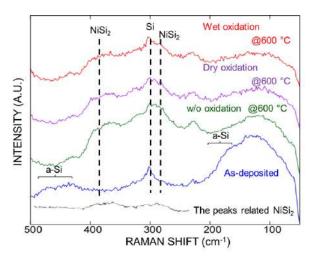

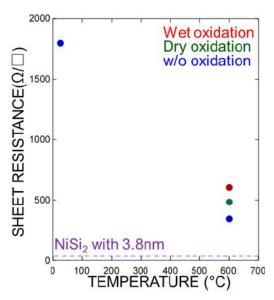

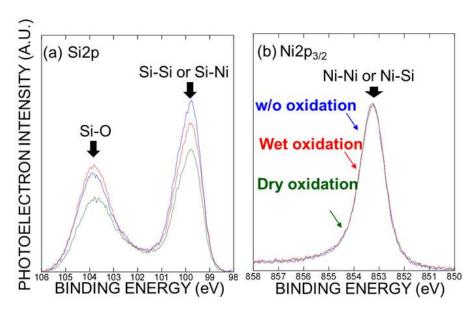

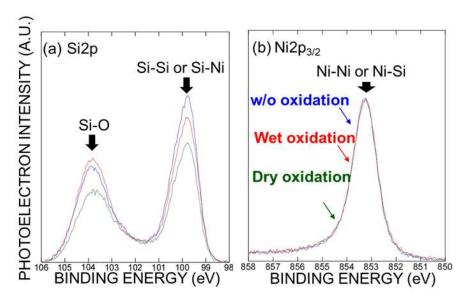

| 15 | 23 | 表面酸化処理したSi/Ni/Si構造の熱処理によるSiO2上への極薄NiSi2膜形成                                    | 名大    | 木村 圭佑 |

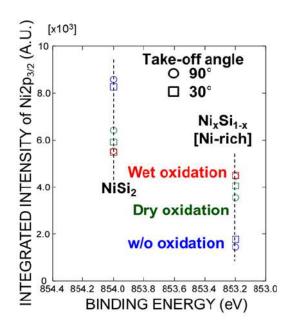

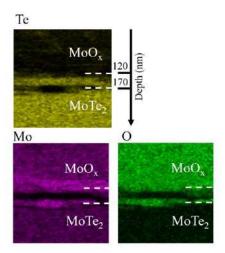

| 16 | 18 | Ar イオン注入した多層 MoTe 2の熱処理によるテルルナノシート形成                                          | 東京都市大 | 村中 柊都 |

| 17 | 29 | 2層MoS <sub>2</sub> /h-BN MISキャパシタでの界面準位密度の測定                                  | 千葉大   | 鶴岡 大樹 |

| 18 | 36 | ALDの実現に向けたオゾン処理と真空アニールによる $WSe_2$ 表面への $Se$ 欠陥導入                              | 千葉大   | 小島 拓也 |

| 19 | 27 | 4H-SiC/SiO <sub>2</sub> 界面におけるバンド配列の理論解析:界面双極子形成の検討                           | 三重大   | 松田 隼  |

| 20 | 13 | GaN-MOS界面の酸化ガリウム層における原子配列評価                                                   | 産総研   | 上沼 睦典 |

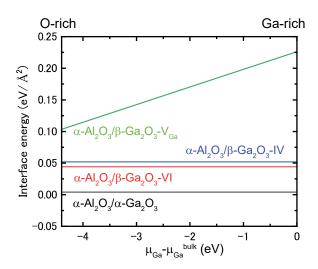

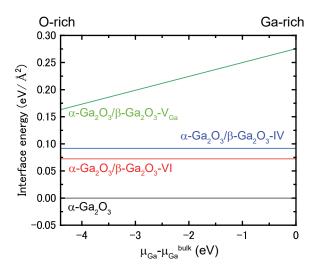

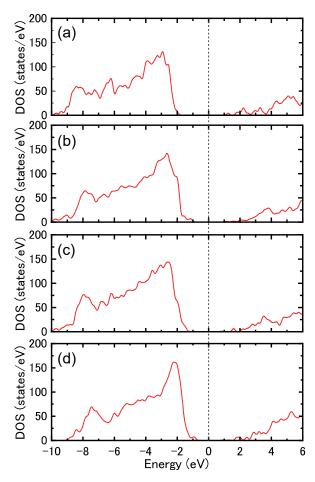

| 21 | 42 | 界面エネルギー計算にもとづく $\alpha$ -Al $_2$ O $_3$ (0001)基板上Ga $_2$ O $_3$ の 構造安定性の理論的検討 | 三重大   | 戸田 康太 |

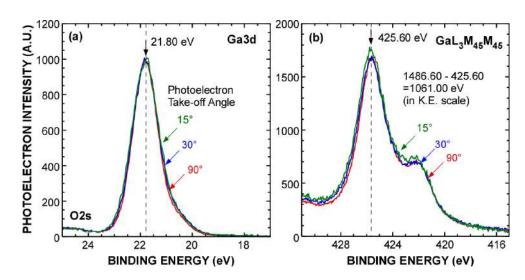

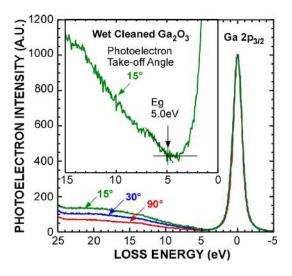

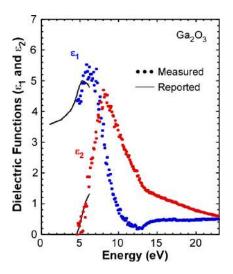

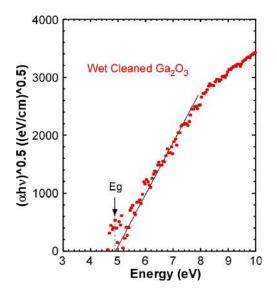

| 22 | 41 | 化学溶液洗浄したβ-Ga <sub>2</sub> O <sub>3</sub> 表面の光電子分光分析                           | 福岡大   | 大田 晃生 |

### EDIT29

# 半導体製造における分析・計測技術の最前線

2024/1/31

株式会社 日立製作所 研究開発グループ **人見敬一郎**

### 1 自己紹介

2005年4月 (株)日立製作所入社 レジスト材料の高精度計測に従事

2010年10月 NY州Albany NanotechにてIBMとの共同研究に従事

2015年2月 電子顕微鏡の電子銃開発に従事

2016年4月 (株)日立ハイテクにて先端装置開発に従事

2020年4月 (株)日立製作所 電子顕微鏡の研究グループ マネージャを拝命

### 2 背景

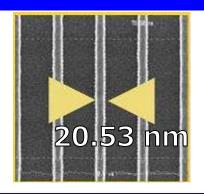

### ●半導体回路パターンの長さを計測するための走査電子顕微鏡の開発に従事

### 装置外観

### 半導体回路パターンの例

### 装置性能

空間分解能: 1.65 nm

: 1.35 nm(画像処理)

計測再現性: 0.12 nm

装置間機差(目標値): 0.1 nm

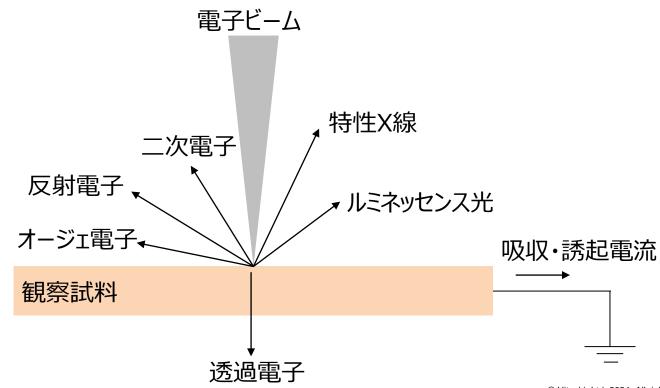

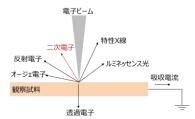

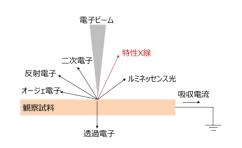

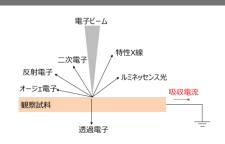

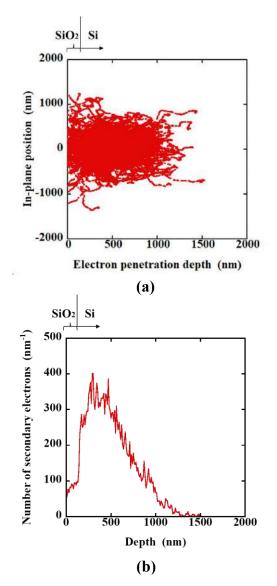

### 3 電子ビーム照射により生じる信号

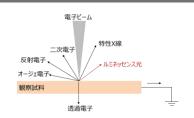

- ●電子ビーム照射により、試料からは下図のような信号が発生する

- ●信号量・特性は観察試料の形状・材料に依存するため、目的に応じて信号検出

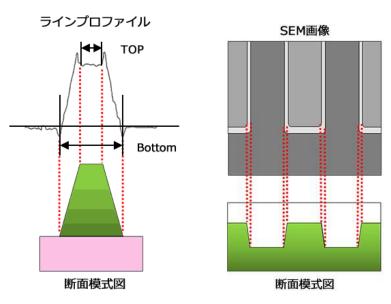

### 4 二次電子の応用(1)

### ●二次電子は試料形状により信号量が変化する →形状計測、欠陥検査に応用される

日立ハイテク Webサイトから抜粋

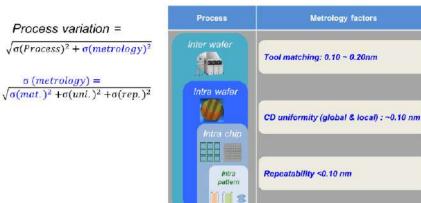

Fig. 12 Budget analysis of metrology errors for process control

### CD-SEMに求められる計測性能

Zhigang Wang et al. "What is prevalent CD-SEM's role in EUV era?" SPIE 2020

### 5 二次電子の応用(2)

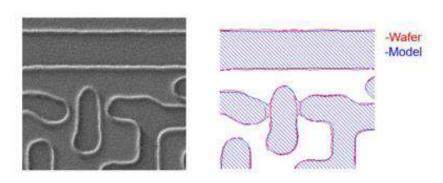

### ●二次電子は試料形状により信号量が変化する →形状計測、欠陥検査に応用される

Figure 6 Local variation dominates EPE in 1st litho-etch layer, contributing >35% of total EPE budget Wenxhan Zhou et al. "Contour-based metrology for assessment of edge placement error and its decomposition into global/local CD uniformity and LELE intralayer overlay" SPIE 2021

パターン輪郭計測への応用例

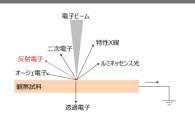

### 6 反射電子の応用

### ●反射電子は試料材料により信号量が変化する →形状計測、材料特性計測に用いられる

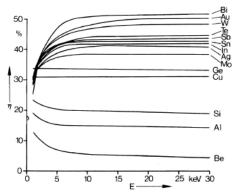

Fig. 4.9. Backscattering coefficient  $\eta$  as a function of electron energy in the range 1–30 keV [4.5]

Reimer著

"Scanning electron Microscopy"より

重い元素ほど反射電子が多くなる

Ofer Adan et al. "A yield-centric perspective on the growing eBeam role in patterning control" SPIE 2021

下層に埋まったGAA構造の可視化

### 7 ルミネッセンス光の応用

●ルミネッセンス光は電子線照射により励起された電子がエネルギーを失うときに発生する光。励起準位により波長が変化する → 組成分析、欠陥検査に用いられる

TiO<sub>2</sub>のカソードルミネッセンス観察例 日立ハイテクWebサイトより

#### 欠陥評価:エピタキシャル層の欠陥計数

カソードルミネッセンス強度イメージ(365 nm)

GaNの貫通転移可視化例 東京インスツルメンツ社Webサイトより

### 8 特性X線の応用

●特性X線は電子線照射により励起された電子がエネルギーを失うときに発生するX線。励起準位により波長が変化する

→ 組成分析に用いられる

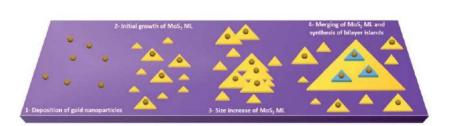

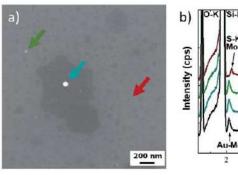

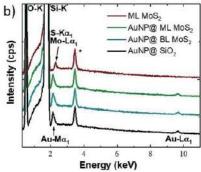

Fig. 3 (a): SEM image where the arrows indicate the sites of the EDX spectra. (b) EDX spectra of ML MoS $_2$  (red line), gold NPs on ML MoS $_2$  (green line) and on BL MoS $_2$  (cyan line) and the reference of gold NPs on the SiO $_2$  substrate (black line), respectively. The asterisk indicates a peak due to the instrumental system.

L. Seravalli et al., Nanoscale Advances 3,4826(2021).

特性X線によるMoS2の可視化例

### 9 吸収・誘起電流の応用

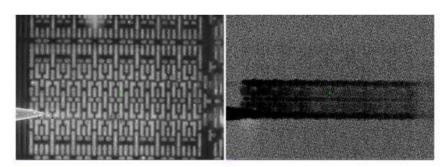

●電子線照射により試料内部に生じる電荷量をイメージング →試料内部の導通状態を可視化する

Fig. 7. SEM (left) and EBIC (right) images of an SRAM cell analyzed at 1.0 kV with the probe on a VDD contact. A "dark" zone extends down two NW/PW boundaries close to the contact.

### SRAMセルの可視化例

G. M. Johnson, IEEE IPFA2020

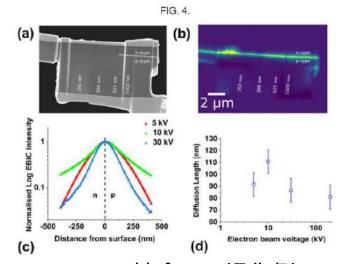

p-n接合の可視化例

E.B. Yakimov, CRYSTALLOGRAPHY REPORTS 66, p. 581-593(2021)

# HITACHI Inspire the Next

### 原子層堆積法によるナノシート酸化物半導体トランジスタ

### A nanosheet oxide-semiconductor transistor using atomic layer deposition

小林 正治 <sup>1,2</sup> 日掛 凱斗 <sup>2</sup>, 李 卓 <sup>2</sup>, ハオ ジュンシャン <sup>2</sup>, パンディ チトラ <sup>2</sup>, 更屋 拓哉 <sup>2</sup>, 平本 俊郎 <sup>2</sup>, 高橋 崇典 <sup>3</sup>, 上沼 睦典 <sup>3</sup>, 浦岡 行治 <sup>3</sup>

1 東京大学工学系研究科附属システムデザイン研究センター 〒153-8505 東京都目黒区駒場 4-6-1 2 東京大学生産技術研究所株式会社 3 奈良先端科学技術大学院大学

Masaharu Kobayashi<sup>1,2</sup>, Kaito Hikake<sup>2</sup>, Zhuo Li<sup>2</sup>, Junxiang Hao<sup>2</sup>, Chitra Pandy<sup>2</sup>, Takuya Saraya<sup>2</sup>, Toshiro Hiramoto<sup>2</sup>, Takanori Takahashi<sup>3</sup>, Mutsunori Uenuma<sup>3</sup>, and Yukiharu Uraoka<sup>3</sup>

1 System Design Lab, The University of Tokyo, 4-6-1 Komaba Meguro-ku, Tokyo 153-8505, Japan

2 Institute of Industrial Science, The University of Tokyo, 3 Nara Institute of Science and Technology Tel:+ 81-3-5452-6813, Fax: + 81-3-5452-6265 (e-mail: masa-kobayashi@nano.iis.u-tokyo.ac.jp)

#### **Abstract**

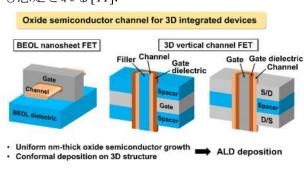

3D integration has been actively explored for high density and high functionality of semiconductor devices. In particular, 3D monolithic integration builds a memory array directly on top of a processing unit and thus enables high energy-efficient computing. Oxide semiconductor is a promising channel material for 3D integration due to its low temperature process, high mobility and low leakage. Highly uniform and high quality oxide semiconductor deposition is necessary. In this paper, we developed atomic layer deposition (ALD) process of nanosheet InGaOx (IGO) with high quality and high uniformity. We investigated the composition and thickness dependence of IGO FET characteristics. We demonstrated high mobility, normally-off, high reliability nanosheet IGO FET.

#### 1. 背景

半導体デバイスの大規模集積化に向けて、デ バイスの高密度化・高機能化・高製造可能性を 実現できる三次元集積デバイス技術が重要と なってきている.従来ディスプレイ応用で用い られてきた InGaZnO を始めとする酸化物半導 体チャネルのトランジスタ(OSFET)は、低温で CMOS プロセスの配線層に形成可能であり[1-6], 三次元構造メモリへの適応可能性も示唆さ れており[7,8]有望視されている(図1). 低温形 成可能な他、高移動度・低リーク電流・高耐圧 といった優れた特徴も有している. OSFET の大 規模集積化には微細化が必須であり、薄膜トラ ンジスタである以上、短チャネル効果を抑制す るためには極薄膜の成膜が必須である. OS の 場合,原子層堆積(ALD)法を用いた成膜が可能 である[9]. 私達は, CMOS プロセスとの整合性 を考慮し, 高温での材料の安定性を重視し, 高 温でもアモルファス相を維持できるとされる InGaO(IGO)に注目している. これまで ALD 法による InGaO を用いた OSFET の基礎的な特性の報告[10]はあるものの、大規模集積化に向けたデバイス設計に資する研究報告はされていない. また OSFET の製造プロセスでは酸素を意図的に導入することが想定されるため、酸化による影響を受けにくい酸化物ベースの電極も想定される[11].

図 1 酸化物半導体の三次元集積デバイスへの応用可能性

本研究では、チャネル材料として IGO、電極材料として InSnO(ITO)を ALD 法で成膜する技術を開発し、IGO FET の組成比・膜厚依存性などを系統的に評価して特性間のトレードオフを調査し、高性能・高信頼性なナノシート IGO OSFET を開発したので報告する.

#### 2. 酸化物半導体の ALD 成膜とデバイス試作

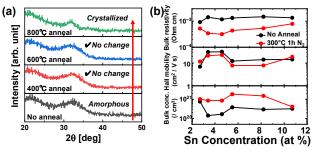

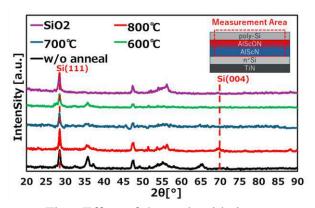

本研究では、IGO および ITO を熱 ALD 法により成膜した.プリカーサーとしては、TEIn、TEGa、TESn を用い、酸化剤としては O3 を用いた.成膜温度は 250 $^{\circ}$ Cである.はじめに IGO の熱安定性を調べるために,成膜後アニール (PDA)を行い、XRD 測定を行った.図 2(a)に示すように、短距離秩序を表すハローパターンが見えるが 600 $^{\circ}$ Cまでアモルファス相が維持されていることがわかる.次に ITO の電気特性を調べるために、In と Sn の組成比を変えたサンプルを用意し、ホール測定を行った.図 2(b)に示すように、Sn が 5 $^{\circ}$ Cであるときにキャリア密度が最大で抵抗率が最小になり、PDA によって特性が向上することもわかった.

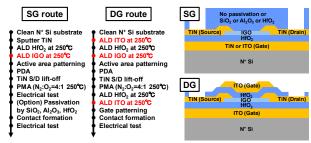

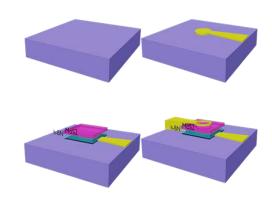

今回、シングルゲートとダブルゲートの IGO FET を試作した。シングルゲートでは、スパッタで成膜した TiN をボトムゲートとし、ALD 法で成膜した HfO2 をゲート絶縁膜とし、ALD 法で IGO を成膜しパターニングを行った。IGO については後述のように組成比および膜厚をふっている。 TiN のリフトオフによりソース・ドレインのパッドを形成した。ダブルゲートでは、ボトムゲートに ALD 法による ITO を用いたシングルゲートのプロセスに続いて、トップゲートを ALD 法で成膜した HfO2 と ITO で形成して試作を行った。

図 2 (a) IGO 薄膜の PDA 後の XRD スペクトル, (b)ITO 薄膜のホール測定による特性の組成比依存性.

図3 シングルゲートおよびダブルゲート IGO FET の試作プロセスフローとデバイス断面模式図.

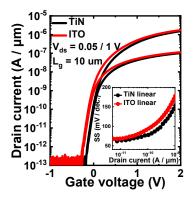

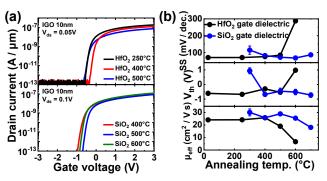

#### 3. シングルゲート IGO FET のデバイス特性

はじめに典型的な IGO FET の  $I_{d}$ - $V_{g}$  特性を図 4 に示す. TiN ゲート・ITO ゲートいずれにも良好なトランジスタ特性を示しており,ほぼ理想的なサブスレショルド係数(SS)を有している. IGO FET の熱安定性を見るために,IGO FET のPDA 温度依存性を図 5 に示す.  $HfO_2$  のゲート絶縁膜で少なくとも 500 でまで安定に動作していることがわかる. 500 でより高温での特性劣化は, $HfO_2$  の膜厚が 12nm 程度と厚いため結晶化してしまったことが原因である. 実際に参考として  $SiO_2$  をゲート絶縁膜とすると 600 でまで安定である.

図 4 TiN と ITO をゲートとする IGO FET の Id-Vg 特性.

図 5 IGO FET の I<sub>d</sub>-V<sub>g</sub> 特性の PDA 温度依存性.

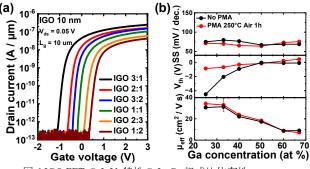

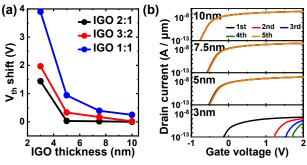

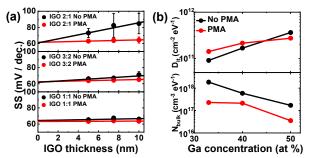

続いて In/Ga 組成比依存性を調査した. 図 6 には 10nm の膜厚の IGO FET で In/Ga 組成比を 3:1 から 1:2 までふったものの特性を示す. Ga 濃度を増加するにつれて移動度が下がり,閾値電圧( $V_{th}$ )は高くなることがわかる. サブスレショルド係数は大きく変化しない. これらは,In を含む酸化物半導体では通常 InO のネットワークが電子伝導に寄与する一方,GaO がこのネットワークに導入されることで電子伝導が抑制されることが原因と考えられる[12,13]. 電極形成後アニール(PMA)後には,特に In 濃度が高い IGO FET で  $V_{th}$  が高くなっている. これはドナーとして働く酸素空孔が PMA によって減少したことによると考えられる.

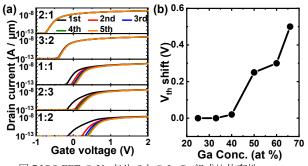

Ga 濃度を増加させたときに顕著になるのが  $V_{th}$  のドリフトである. 図 7 にゲート電圧を複数 回掃引した時のトランジスタ特性を示す. Ga 濃度を増加するほど  $V_{th}$  の正方向へのドリフトが顕著になる. 一方 SS は小さくなっていることもわかる. このため,ノーマリーオフ動作のために Ga 濃度を増やしたいが, $V_{th}$  ドリフトを考えると Ga は 40%までが許容範囲といえる.

図 6 IGO FET の I<sub>d</sub>.V<sub>g</sub> 特性の In:Ga 組成比依存性

図 7 IGO FET の V<sub>th</sub> ドリフトの In:Ga 組成比依存性

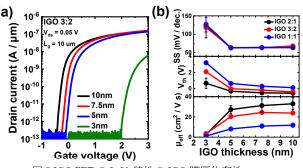

次に IGO の膜厚依存性を調査した. 図 8 に In:Ga=3:2 の組成で膜厚を 10nm から 3nm まで ふったものの電気特性を示す. 膜厚を 5nm 程度 まで薄くしても電気特性が維持できていることがわかる. 一方, 今回の実験では 3nm まで薄

くすると特性が劣化していることがわかる. IGOの極薄化による特性劣化が本質的な物理によるものかは現在調査中である。

$V_{th}$  のドリフトには IGO の膜厚依存性があることもわかった. 図 9 に図 7 と同じく,ゲート電圧を複数回掃引したときの  $V_{th}$  のドリフトの IGO 膜厚依存性を示す. IGO の膜厚が薄いほどドリフトが大きいことがわかる.  $V_{th}$  のドリフトも考慮すると IGO の膜厚は 5-7.5nm 程度が適切な範囲といえる.

図 8 IGO FET  $\mathcal{O}$   $I_{d}$ - $V_{g}$  特性 $\mathcal{O}$  IGO 膜厚依存性

図 9 IGO FET の V<sub>th</sub> ドリフトの IGO 膜厚依存性

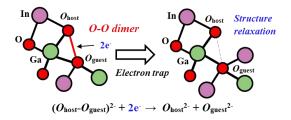

IGO FET の V<sub>th</sub>のドリフトについては(1)Ga 濃 度が増加するにつれて大きくなる, (2)IGO 膜厚 が薄くなるにつれて大きくなる,ことが以上よ りわかった. この現象については過去の報告に 基づいて以下のように解釈できる(図 10)[14]. IGOには成膜またはアニール時に取り込まれる 過剰酸素が存在する. この過剰酸素はバンドギ ャップ内の伝導帯側に状態密度を形成しキャ リア電子をトラップする. そのため最初のゲー ト電圧掃引では Vth は低いが SS が大きくなる. しかしこの過剰酸素は隣接しているホスト酸 素とダイマー結合していると、キャリアをトラ ップすることでダイマーが切断され構造緩和 が起こり、その結果バンドギャップ内の伝導帯 側にあった状態密度がバンドギャップ内の深 いところへ遷移する. これにより二回目以降の 電圧掃引では Vth は高くなり SS が小さくなる.

このダイマーの切断は酸素との結合が強い Ga が酸素に接続しているほど起こりやすくなるため、Ga 濃度が高いほど  $V_{th}$  ドリフトが大きくなると考えられる. IGO の膜厚が薄い場合には、大気中の水分を含む空気が IGO と接しており、プロセス中の加熱より酸素が IGO 中に取り込まれ、膜厚が薄いほど過剰酸素がチャネル近傍に形成されやすくなり、キャリア電子のトラップが容易となり、 $V_{th}$  ドリフトが起こりやすくなるものと考えられる.

図 10 IGO FET における V<sub>th</sub> ドリフトの説明図

これまで IGO の膜内の電荷トラップに着目してきたが、今回ゲート絶縁膜と IGO チャネルとの間の界面準位密度も評価した. SS の IGO 膜厚依存性を取得しそれを線形フィッティングすることにより、膜厚によらない成分(界面準位相当)と膜厚による成分(IGO 膜中トラップ相当)を抽出した. 図 11 に示すように、界面準位密度は Ga の濃度にはほとんど依存せず $10^{11}$ cm<sup>-2</sup>eV<sup>-1</sup>となり、 $HfO_2$ ゲート絶縁膜に対して良好な値を示している. これは酸化膜-酸化膜という材料の相性の良さを端的に表しているものと考えられる.

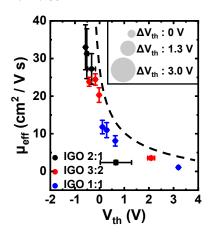

以上の結果を移動度、 $V_{th}$ 、 $V_{th}$  ドリフトについてまとめたのが図 12 である. これらの間には明らかなトレードオフが存在し、高い移動度とノーマリーオフ動作、そした高い信頼性を同時

に実現するためにはこのトレードオフを解消する必要があり、プロセスの最適化またはデバイス構造を変えることが求められる。本研究では特に後者のアプローチをとり、ダブルゲートのナノシート IGO FET 構造を採用することによって高い移動度とノーマリーオフ動作、そして高信頼性を実現することを試みたので次章で説明する。

図 11 (a) IGO FET の SS の膜厚依存性, (b)抽出した界面準位密度と バルクトラップ密度.

図 12 IGO FET の移動度, V<sub>th</sub>, V<sub>th</sub> ドリフトの関係.

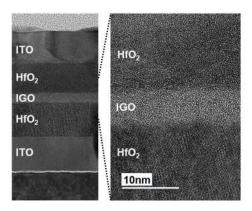

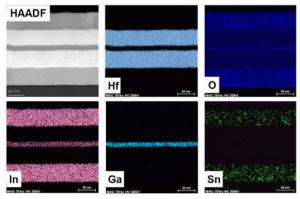

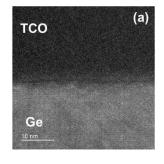

#### 4. ダブルゲートナノシート IGO FET

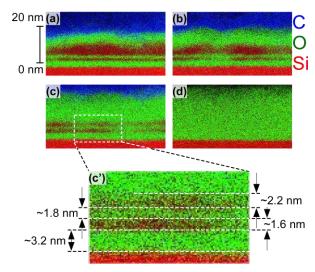

試作したダブルゲートナノシート IGO FET のチャネル部の断面 TEM 像と EDX 元素マッピングを図 13, 14 に示す. IGO の膜厚は 7nm であり, ALD 法により均一かつ平坦にアモルファス相として形成できていることがわかる. またHfO2 と IGO の界面は急峻であり, ITO に Sn が一様に分布していることも確認できる.

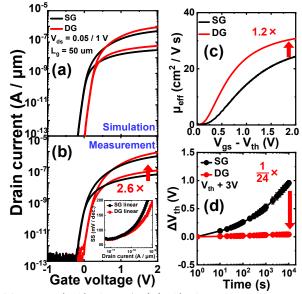

次に試作したダブルゲートナノシート IGO FET の電気特性を図 15 に示す. シングルゲートと比べて  $V_{th}$  が高くなり,ノーマリーオフ動作が得られていることがわかる. これは,ダブルゲートにすることで各ゲートが IGO チャネル膜厚の半分をピンチオフするだけでよくな

図 13 IGO FET のチャネル部の断面 TEM 像.

図 14 IGO FET のチャネル部の EDX 元素マッピング.

図 15 シングルゲート(SG)とダブルゲート(DG)IGO FET  $\sigma$   $I_d$ - $V_g$ 特性(a)TCAD シミュレーション, (b)測定結果, (c)移動度, (d)正バイアスストレス  $V_h$ シフト.

るために  $V_{th}$  が高くなるからである. 実際に TCAD シミュレーションでも確認している. ダブルゲートでチャネルが上下二層になったことでオン電流は 2.6 倍向上している. 移動度はシングルゲートに比べて 1.2 倍向上している.

これは上部の $HfO_2$ を成膜する前に真空 $N_2$ アニールを施しているため、過剰酸素を抑制できたことが一因と考えられる。特筆すべきは正電圧ストレスによる $V_{th}$ シフトが大幅に改善されたことである。これはダブルゲートナノシート構造にすることで過剰酸素が抑制できたこと,そしてストレス電界が低減できたことが要因と考えられる。

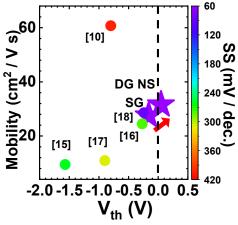

最後に図 16 に ALD で成膜した IGO による FET のベンチマークを示す[10,15-18]. 本研究では、ダブルゲートナノシート IGO FET により高 移動度・ノーマリーオフ動作・高信頼性を同時に実現することに成功した.

図 16 ALD 法による IGO FET の特性のベンチマーク

#### 5. まとめ

本研究では、モノリシック三次元集積デバイスとして期待される酸化物半導体トランジスタに関して、チャネル材料として高い熱安定性を有する IGO に注目し、ALD 法によるナノ薄膜の成膜技術を開発、IGO FET のトランジスタ特性について IGO の組成比依存性や膜厚依存性を系統的に調査し移動度・ $V_{th}$ ・ $V_{th}$ 安定性の間に明確なトレードオフがあることを明らかにし、ダブルゲートナノシート IGO FET で高移動度・ノーマリーオフ動作・高信頼性を実現した.本発表は VLSI Symposium 2023 で発表した内容に基づく[19].

#### 謝辞

本研究は TSMC Advanced Semiconductor Research Project と科研費(21H04549 の支援を受けて実施された.

#### 文献

- [1] H. Ye et al., "Double-Gate W-Doped Amorphous Indium Oxide Transistors for Monolithic 3D Capacitorless Gain Cell eDRAM", IEDM, 613 (2020).

- [2] J. Wu et al., "Monolithic Integration of Oxide Semiconductor FET and Ferroelectric Capacitor Enabled by Sn-Doped InGaZnO for 3-D Embedded RAM Application", IEEE TED, 68, 12 (2021).

- [3] U. Chand et al., "2-kbit Array of 3-D Monolithicallystacked IGZO FETs with Low SS-64mV/dec, Ultra-lowleakage, Competitive μ-57 cm²/V-s Performance and Novel nMOS-Only Circuit Demonstration", VLSI Symp., T10-2 (2021).

- [4] Z. Lin et al., "High-Peformance BEOL-Compatible Atomic-Layer-Deposited In2O3 Fe-FETs Enabled by Channel Length Scaling down to 7 nm: Achieving Performance Enhancement with Large Memory Window of 2.2 V, Long Retention > 10 years and High Endurance > 10<sup>8</sup> Cycles", IEDM, 386 (2021).

- [5] M. Endo et al., "A c-axis aligned crystalline IGZO FET and a 0.06-μm² HfO₂-based Capacitor 1T1C FeRAM with High Voltage Tolerance and 10-ns Write Time", IEDM 2022, 134 (2022).

- [6] S. Subhechha et al., "Ultra-low Leakage IGZO-TFTs with Raised Source/Drain for Vt > 0 V and Ion > 30  $\mu$ A/ $\mu$ m", VLSI Symp., 292 (2022).

- [7] Z. Li et al., "A 3D Vertical-Channel Ferroelectric /Anti-Ferroelectric FET With Indium Oxide", IEEE EDL, 43, 8, 1227 (2022).

- [8] K. Huang, et al., "Vertical Channel-All-Around (CAA) IGZO FET under 50 nm CD with High Read Current of 32.8 μ A/μ m (Vth + 1 V), Well-performed Thermal Stability up to 120 °C for Low Latency, High-density 2T0C 3D DRAM Application", VLSI Symp., 296 (2022).

- [9] J. Sheng et al., J. Vac. Sci. Technol. A, "Review Article: Atomic layer deposition foroxide semiconductor thin film transistors: Advances in research and development", 36, 6, 060801 (2018).

- [10] H. J. Yang et al., "High-Performance Thin-Film Transistors with an Atomic-Layer-Deposited Indium Gallium Oxide Channel: A Cation Combinatorial Approach", ACS AMI, 12, 47, 52937-52951 (2020).

- [11] J. W. Elam, et al., "Atomic Layer Deposition of Indium Tin Oxide Thin Films Using Nonhalogenated Precursors", J. Phys. Chem. C, 112, 1938 (2008).

- [12] T. Kamiya et al., "Origins of High Mobility and Low Operation Voltage of Amorphous Oxide TFTs: Electronic Structure, Electron Transport, Defects and Doping" J. Disp. Tech., 5, 12, 468 (2009)

- [13] S. L. Moffitt, et al., "Probing the Unique Role of Gallium in Amorphous Oxide Semiconductors through Structure— Property Relationships", Adv. Electron. Mater., 3, 1700189 (2017).

- [14] W. H. Han et al., "Electronic Structure of Oxygen Interstitial Defects in Amorphous In-Ga-Zn-O Semiconductors and Implications for Device Behavior", Phys. Rev. Appl., 3, 044008 (2015).

- [15] J. Sheng et al., "Atomic Layer Deposition of an Indium Gallium Oxide Thin Film for Thin-Film Transistor Applications", ACS AMI, 9, 28, 23934-23940 (2017).

- [16] H. J. Seul et al., "Atomic Layer Deposition Process-Enabled Carrier Mobility Boosting in Field-Effect Transistors through a Nanoscale ZnO/IGO Heterojunction", ACS AMI, 12, 30, 33887-33898 (2020).

- [17] T. Hong et al., "Significance of Pairing In/Ga Precursor Structures on PEALD InGaOx Thin-Film Transistor", ACS AMI, 13, 24, 28493-28501 (2021).

- [18] J. Zhang et al., IEEE EDL, pp 273-276 (2023).

- [19] K. Hikake et al., "A Nanosheet Oxide Semiconductor FET Using ALD InGaOx Channel and InSnOx Electrode with Normally-off Operation, High Mobility and Reliability for 3D Integrated Devices", VLSI Symp. T14-1 (2023).

### 原子層堆積法で成膜した非晶質/多結晶 In-Ga-O トランジスタの信頼性

# Reliability characteristics in atomic layer deposited amorphous/polycrystalline In-Ga-O

髙橋 崇典1, 上沼 睦典2, 小林 正治3, 浦岡 行治1

- 1 奈良先端科学技術大学院大学 〒630-0192 奈良県生駒市高山町 8916-5

- 2 産業技術総合研究所 〒841-0052 佐賀県鳥栖市宿町 807-1

- 3 東京大学 〒153-8505 東京都目黒区駒場 4-6-1

Takanori Takahashi <sup>1</sup>, Mutsunori Uenuma <sup>2</sup>, Masaharu Kobayashi <sup>3</sup>, Yukiharu Uraoka <sup>1</sup> *1 Nara Institute of Science and Technology, 8916-5 Takayama-cho, Ikoma, Nara, 630-0192, Japan 2 Advanced industrial Science and Technology, 807-1 Shuku-machi, Tosu, Saga, 841-0052, Japan*

3. The University of Tokyo, 4-6-1 Komaba, Meguro-ku, Tokyo, Japan Tel:+ 81-72-6063, (e-mail:t.takahashi@ms.naist.jp)

#### **Abstract**

This paper discusses reliability characteristics for positive gate bias stress of field-effect transistors with atomic layer deposited amorphous or crystalline In-Ga-O oxide semiconductor channels. The shift in threshold voltage of amorphous In-Ga-O were primarily determined by composition ratio of In:Ga and annealing temperature base on excess oxygen model. In addition, there is a concern that atomic layer deposited In-Ga-O is more likely to incorporate excess oxygen into thin film due to its oxidation process compared to conventional sputtering methods. To solve this issue, crystalline In-Ga-O was proposed, and its atomic layer deposition and device application were demonstrated. The crystalline In-Ga-O, Ga-doped In<sub>2</sub>O<sub>3</sub> channel achieved better reliability characteristics for gate bias stress compared to amorphous In-Ga-O channel. This result suggests that the lower Ga concentration and crystal phase of bixbyite In<sub>2</sub>O<sub>3</sub> suppressed introduction of excess oxygen. The use of crystalline material is an important approach to achieve both high-mobility and high-reliability in atomic layer deposited oxide semiconductors for integrated device applications.

#### 1. はじめに

$In_2O_3$ や ZnO を主成分とする酸化物半導体を用いた電界効果トランジスタ (FET) は 10-50 cm²/Vs を超える電子移動度、極小リーク電流、低プロセス温度等の特徴から薄膜トランジスタのチャネル材料として実用化されている。近年、In-Ga-Zn-O (IGZO) $^{[1]}$  等に代表される酸化物半導体は超集積回路や半導体メモリへの実装が期待されており、三次元強誘電体メモリ $^{[2,3]}$  や Back end of line  $^{\sim}$  適用可能な  $FET^{[4-8]}$  が実証されている。酸化物半導体を用いた各種集積デバイスを実現するためには、素子の集積度と短チャネル効果抑制の観点から極薄膜チャネルを三次元構造上 $^{\sim}$  とのスパッタ法ではなく原子層堆積 (ALD)

法を用いる必要がある。しかし、これまでは酸化物半導体の成膜に物理的成長法であるスパッタ法が用いられてきたため、ALDプロセスが酸化物半導体の物性や FET の信頼性へ及ぼす影響、それらの相関関係は明らかではない。したがって、集積デバイスに酸化物半導体を実装するためには、ALD 法によって成膜される酸化物半導体の物性および素子特性プロセスを理解して更なる電子移動度と信頼性の向上を図る必要がある。

本研究グループでは三次元集積デバイスに適用可能な酸化物半導体材料の候補として、過剰な酸素欠損を抑制でき熱プロセス耐性にも優れた非晶質 In-Ga-O (IGO) 系に着目しており、ALD 法による成膜およびデバイス応用を行ってきた[8-10]。しかし、IGO-FET はゲート電圧ス

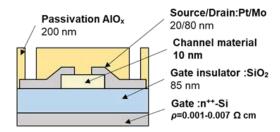

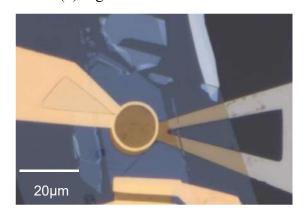

Fig.1 Device structure of IGO-FETs.

Fig.2 Schematic concept of atomic layer deposition of In-Ga-O thin films by super-cycle method.

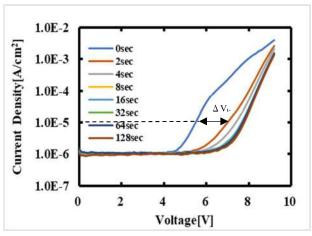

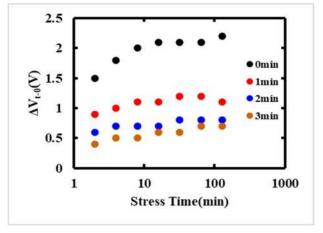

トレスに対して容易にしきい値電圧  $(V_{th})$  が変動することが観測されており、信頼性面に課題がある $^{[8,10]}$ 。本研究では FET の信頼性と半導体材料に由来する IGO 組成比や熱処理温度との関係、結晶化が及ぼす効果を評価することで、 $V_{th}$ 不安定性の要因を考察し、その改善を図ることを目的とする。

#### 2. 実験条件

約 10 nm 厚の IGO チャネルを熱酸化 SiO<sub>2</sub> (85 nm) /n<sup>++</sup>-Si 基板上に ALD 法を用いて成膜し、AlO<sub>x</sub> 保護膜を有するトップコンタクト/ボトムゲート型 FET (図 1) を作製した。IGO チャネルの前駆体には Triethylindium と Trimethylgalliumを使用し、成膜温度は 200℃、酸化剤は O<sub>2</sub> プラズマとした。IGO チャネルの堆積後、大気雰囲気にて熱処理を行った。図 2 に示すように IGO膜における In:Ga の組成比は、InO<sub>x</sub> 層と GaO<sub>x</sub>

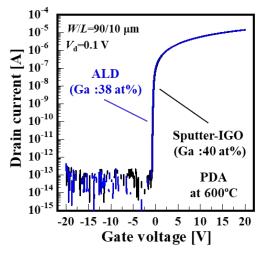

Fig.3 Transfer characteristics of IGO-FETs with ALD (bule line) and sputter (black line) -derived channels.

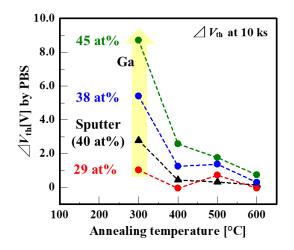

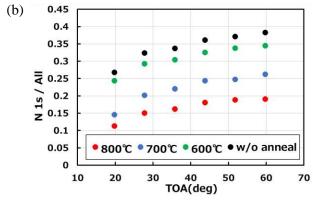

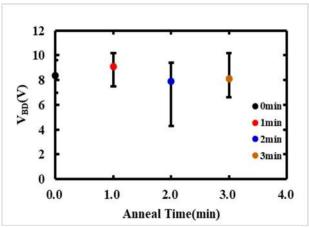

Fig.4 The shift in  $V_{th}$  against annealing temperature of atomic layer deposited amorphous IGO channel with various Ga concentrations.

層の成長サイクル比を調整することで制御した。また、比較試料としてスパッタ法で成膜した各種酸化物半導体材料を用いた FET も作製した。FET の信頼性評価としてはゲート電極に正電圧を印加するポジティブバイアスストレス (positive bias stress:PBS) を実施し、ストレス印加時間に対する  $V_{th}$  シフト量 ( $\triangle V_{th}$ ) を評価した。

#### 3. 実験結果

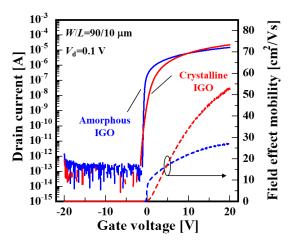

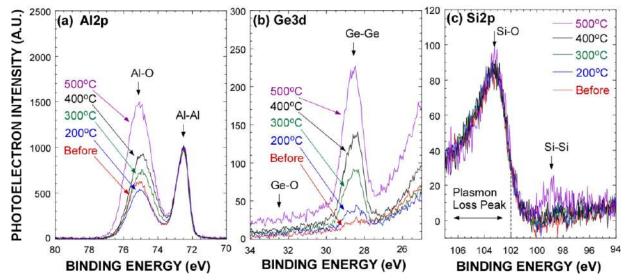

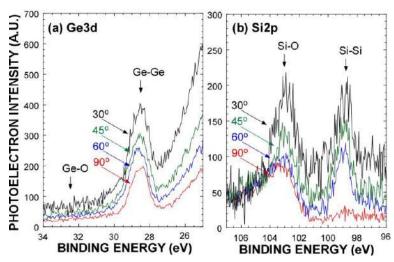

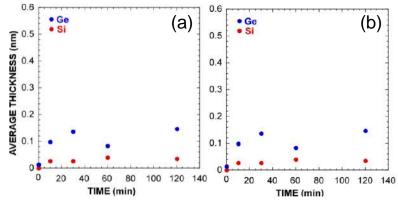

図 3 にスパッタ法および ALD 法によって成

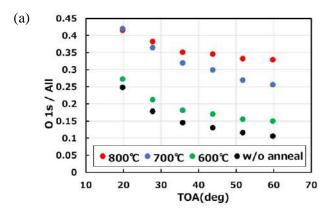

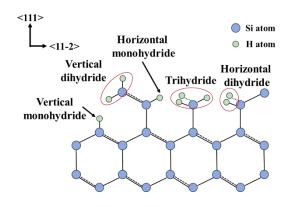

Fig.5 Schematic concept of O-O dimer model as an excess oxygen in amorphous oxide semiconductors.

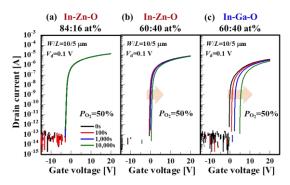

Fig.6 The transfer characteristics of (a) In-Zn-O [In:Zn=84:16 at%], (b) In-Zn-O [In:Zn=60:40 at%], and (c) In-Ga-O [In:Ga=60:40 at%] channels under positive gate bias stress.

膜した非晶質 IGO をチャネルとした FET の伝 達特性を示す。図3より、成膜方法に依存せず 電界効果移動度  $(\mu_{\rm FE})$  、 $V_{\rm th}$ 、S 値がそれぞれ 28.9 cm<sup>2</sup>/Vs、-0.46 V、72 mV/decade であった。図 4 に PBS に対する $\triangle V_h$  の熱処理温度依存性を示 す。ここでは Ga 濃度が異なる ALD-IGO チャネ ルの信頼性を比較した。本研究ではゲート絶縁 膜由来の電荷捕獲成分を最小化するため熱酸 化 SiO<sub>2</sub>を使用おり、電圧ストレスによって発生 する △V<sub>th</sub> は IGO/SiO<sub>2</sub> 界面および IGO 中の欠陥 によって誘発するものとして議論する[11]。図4 より、  $\triangle V_{th}$  は Ga 濃度の増加に伴って増加する こと、IGO チャネルに対する熱処理温度の上昇 に伴って減少することが確認された。また、Ga 濃度が同等程度の ALD 膜 (Ga:38 at%) とスパ ッタ膜 (Ga:40 at%) を比較した場合、熱処理温 度に対して⊿Vth が減少して信頼性が向上する 挙動は一致するが、△Vthの絶対量に差が生じる こと示された。これらの結果から、ALD-IGO 膜 の信頼性は、IGO由来の欠陥、成膜時に導入さ れる欠陥種によって決定することが考えられ

はじめに、IGO における材料由来の欠陥種を 推定するために、過剰酸素モデル<sup>[12]</sup>を導入した。 図 5 に非晶質酸化物半導体における過剰酸素モ

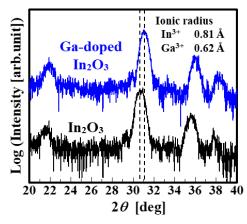

Fig.7 X-ray diffraction profiles of In<sub>2</sub>O<sub>3</sub> and Ga-doped In<sub>2</sub>O<sub>3</sub> deposited by atomic layer deposition.

デルの概念図を示す。非晶質酸化物半導体は構 造自由度が高いため、過剰酸素に対応する O-O 結合の形成エネルギーが単結晶や多結晶構造 と比較して低いことが知られている[13,14]。この 過剰酸素の結合が酸化物半導体の伝導帯直下 にアクセプタ準位を形成するため、電子捕獲の 原因の一つとして考えられている[12-13]。 O-O の 結合力は酸化物半導体の組成に依存すること が予測されており[13]、酸素との結合力が高い金 属元素ほどO-Oの結合力が低下して、電子捕獲 が容易に発生する。この理論計算の予測を検証 するため、酸素との結合エネルギーが低い Zn を含む In-Zn-O 系と信頼性の比較を行った。 こでは、IZOとIGOの成膜にはスパッタ法を用 い、成膜条件は過剰酸素が導入されやすい高酸 素分圧[15]に調整した。図 6 に、IZO (In:Zn=84:16 at%), IZO (In:Zn=60:40 at%), IGO (In:Ga=60:40 at%) の信頼性評価結果を示す。 △Vth は IZO (In:Zn=84:16 at%) < IZO (In:Zn=60:40 at%) < IGO(In:Ga=60:40 at%) の関係を示し、酸素結合エネ ルギーの大きさに依存して PBS に対する信頼 性が変化することが確認され、前述の DFT 計算 の予測と矛盾しないことが示された。また、図 4 において Ga 濃度の上昇に伴う△V<sub>th</sub>の増大が 確認されているが、酸素結合エネルギーの大き な Ga によって過剰酸素の取り込みと電子捕獲 が誘発されていることは明らかである。過去の 報告から、過剰酸素は熱処理温度 450℃ 以上で 脱離が完了することが示されており[12]、図4か ら観測された熱処理温度の上昇に伴って信頼 性が向上する結果とも矛盾しない結果を得た。

Ga 濃度が同等程度の IGO において、成膜方法によって△Vth に差が生じた原因を考察する。 スパッタ法では成膜時の酸素分圧を制御することで膜中の過剰酸素量を制御でき、本研究では十分な熱処理を加えることで高信頼性が得られる条件を用いている。一方で、ALD 法の場

Fig.8 The transfer characteristics of FETs with amorphous (bule lime) and crystalline (red line) In-Ga-O channels.

合は、基板または膜上に吸着した前駆体の有機金属を酸化させるために、成膜中に IGO 膜が O2-plasam に曝露されている。従って、ALD-IGO の成長中に容易に過剰酸素が導入されることが示唆され、過剰酸素量がスパッタ膜よりも過大であったと推察した。ALD 法を用いて非晶質 IGO を成膜する場合は、成長速度を妨げない範囲で酸素分圧や酸化条件を最適化する必要があることが推察される。

以上の結果より、非晶質 IGO 系の PBS に対 する信頼性の特徴として、Ga濃度の増加に伴っ て∠Vthが増大すること、高温熱処理によって∠  $V_{\rm th}$  が減少することが明らかになった。しかし、 Ga 濃度を低減することで信頼性の向上を図る ことは可能であるが、熱処理や各種プロセスに よってキャリア濃度が変動しやすく V<sub>th</sub> の制御 性が低下する課題がある。この課題を解決する ために、In<sub>2</sub>O<sub>3</sub>系結晶性酸化物半導体に着目した。 非晶質  ${f IGO}$  系における  $V_{

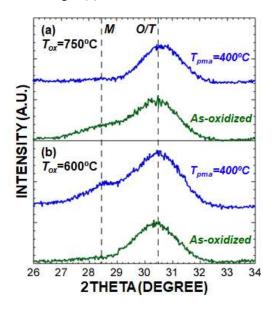

m th}$ の不安定性は過剰酸 素によって律速されるが、過去の研究より結晶 構造を有する InGaZnO (IGZO) や ZnO は非晶質 IGZO よりも過剰酸素の生成エネルギーが低い ことが予測されており[14]、結晶性酸化物半導体 を用いることで ALD によって成膜した酸化物 チャネルの信頼性向上が見込める。本研究では、 Ga を添加した多結晶 In<sub>2</sub>O<sub>3</sub> [[6]を ALD 法によっ て成膜し、非晶質 IGO チャネルと信頼性を比較 することで前述の仮説を検証した。多結晶 IGO を成膜するために、図 2 の成膜条件における InOx:GaOx 比率を Ga 濃度が In2O3 由来のビック スバイト構造が発現する濃度域まで低減させ た。図7にALD法を用いて成膜した結晶性IGO および In<sub>2</sub>O<sub>3</sub> の微小角入射 X 線回折結果を示 す。図7から、IGOはIn2O3を同様のビックス バイト構造を示し、多結晶相を有することを確 認した。また、30° 近傍における 222 ピークに

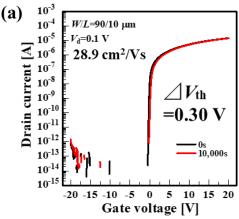

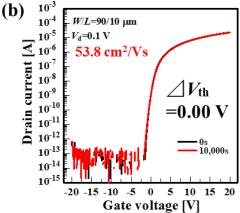

Fig.9 The transfer characteristics FETs of (a) amorphous and (b) crystalline In-Ga-O channels before and after positive gate bias stress.

着目すると、Ga を添加することで高角度側にシフトしており、イオン半径の小さな  $Ga^{3+}$ が  $In_2O_3$  の  $In^{3+}$ サイトに置換型固溶していることが示された。以上より、ALD 法による多結晶 IGO の成長を確認した。

図8に結晶性 IGO をチャネルに用いた FET の伝達特性を示す。多結晶 IGO の  $\mu_{FE}$  は 50cm²/Vs を超えており、非晶質 IGO より高移動 度を達成できることを確認した。図9に、ALD 法で成膜を行った多結晶 IGO および非晶質 IGO をチャネルとする FET の PBS 試験結果を示す。 こでは、IGO チャネルの熱処理温度を 500℃ に設定している。図9より、結晶性 IGO の方が 非晶質 IGO よりも△Vth が小さいことが確認さ れ、高信頼性であることが明らかになった。結 晶性 IGO の適用によって観測された信頼性向 上は、結晶相を用いることによって過剰酸素の 導入が抑制されたこと、Ga 濃度を低減すること による O-O 結合の強化の複合的な要因による ものであると考察した。この実験結果は、IGO 系酸化物半導体の PBS に対する信頼性は過剰 酸素の導入によって律速されること支持して

おり、他の理論計算の予測<sup>[13,14]</sup>と矛盾しない。 また、多結晶 IGO の PBS に対する優れた信頼 性は、熱処理温度 400-700℃ の範囲内で発現す ること確認しており、400℃ 程度の低温プロセ スが要求される BEOL 向けトランジスタ、強誘 電体ゲート FET のような高温熱処理を必要す る各種デバイスに展開できる可能性がある。

以上より、IGO チャネルにおける信頼性はGa濃度、熱処理温度、結晶相によって決定されることを明確化した。さらに、50 cm²/Vs 以上の高移動度と高信頼性を達成するためには、多結晶酸化物半導体を用いることが有効であることを明らかにした。

#### 4. まとめ

IGO系チャネルは膜中の過剰酸素に起因した電子捕獲が発生し、PBSに対する信頼性を悪化させることを実験的に明らかにした。また、IGO系の信頼性向上に向けて結晶性 Ga-doped In<sub>2</sub>O<sub>3</sub>に着目し、ALD法による成膜プロセスを構築した。多結晶 IGOをチャネルとする FET は非晶質 IGOと比較して、移動度と信頼性が優れることを実証した。本研究では、ALD法を用いた酸化物半導体の成膜時は過剰酸素を低減する必要があること、結晶性酸化物半導体は信頼性の更なる向上に有効であること示した。

#### 謝辞

本研究の一部は 科研費 (No. 23K19123、 22H01958)、JST CREST (JPMJCR23A3) の支援 を受けて実施された。

#### References

- [1] K. Nomura et al., *Nature* **432**, 488 (2004).

- [2] M.-K. Kim et al., Sci. Adv. 7, eabe1341 (2021).

- [3] Z. Li et al., *IEEE Electron Device Lett.* **43**, 1227 (2022).

- [4] K. Kaneko et al., 2011 Symposium on VLSI Technology Digest of Technical Papers, 2011, pp. 120-121.

- [5] H. Fujiwara et al., *IEEE Trans. Electron Dev.* **67**, 5329 (2020).

- [6] M. Si et al., *IEEE Trans. Electron Devices* **68**, 6605 (2021).

- [7] J. Wu et al., *IEEE Trans. Electron Dev.* **68**, 6617 (2021).

- [8] K. Hikake et al., 2023 IEEE Symposium on VLSI Technology and Circuits, 2023, pp. 1-2.

- [9] T. Takahashi et al., 第 83 回応用物理学会秋季学術講演会, 21p-B203-19 (2022).

- [10] T. Takahashi et al., 第 70 回応用物理学会秋季学術講演会, 17p-E302-8 (2023).

- [11] K. Nomura et al., *Appl. Phys. Lett.* **95**, 013502 (2009).

- [12] K. Ide et al., Appl. Phys. Lett. **99**, 093507 (2011).

- [13] H. Han et al., *Phys. Rev. Applied* **3**, 044008 (2015).

- [14] J. Robertson and Y. Guo, *Appl. Phys. Lett.* **104**, 162102 (2014).

- [15] K. Ide et al., *Phys. Status Solidi A* **216**, 1800372 (2019).

- [16] K. Ebata et al., Appl. Phys. Exress 5, 011102 (2012).

# 極薄膜 AIN 酸化で生成したワイドバンドギャップ $Al_2O_3$ 膜による リーク電流低減実現

# Reducing Leakage Current in Wide-Bandgap Alumina Films Fabricated Through the Oxidation of Ultrathin AlN Films

中島 裕亮, 高島 章, 野口 将希, 磯貝 達典

キオクシア株式会社 先端メモリ開発センター 三重県四日市市山之一色町 800 Yusuke Nakajima\*, Akira Takashima, Masaki Noguchi, Tatsunori Isogai Advanced Memory Development Center, Kioxia Corp., 800, Yamanoisshiki-cho, Yokkaichi, Mie, 512-8550, Japan (E-mail: yusuke11.nakajima@kioxia.com)

#### **Abstract**

Aluminum oxide (Al<sub>2</sub>O<sub>3</sub>) films were fabricated through the oxidation of ultrathin aluminum nitride (AlN) films. The fabricated films exhibited a leakage current reduction compared to that of conventional Al<sub>2</sub>O<sub>3</sub> films fabricated using atomic layer deposition (ALD). This reduction in the leakage current can be attributed to the formation of  $\theta$ -Al<sub>2</sub>O<sub>3</sub>, which has a wider-bandgap than  $\gamma$ -Al<sub>2</sub>O<sub>3</sub>. The formation of  $\theta$ -Al<sub>2</sub>O<sub>3</sub> was attributed to the residual stress caused by the oxidation of the AlN thin films.

#### 1. はじめに

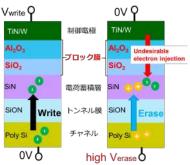

BiCS FLASH™の消去動作の更なる特性向上 のために、メモリセルのブロック膜に用いられ ている Al<sub>2</sub>O<sub>3</sub> の高絶縁化を検討している[1]。 BiCS FLASH™のメモリセルは、チャネル、 ネル膜、電荷蓄積層、ブロック膜、制御電極の スタック構造を有している [2-4]。図 1 は、メ モリセルの書き込みおよび消去動作時の電荷 注入の概略図を示す。書き込み動作は、正電圧 が制御電極側に印加され、電子がチャネルから トンネル膜を介して電荷蓄積層に注入される [5]。消去動作は、正電圧がチャネルに印加され、 書き込み動作時の電子と同様にトンネル膜を 介して正孔が電荷蓄積層に注入される[6]。消去 動作の際、制御電極からブロック膜を介してス タック構造を電子が貫通するほどの高い電圧 を印加すると、チャネルから注入された正孔と 制御電極から注入された電子とが電気的に打 ち消しあうことで、消去がそれ以上進まなくな る課題がある[6]。したがって、消去動作の特性 向上にはブロック膜の高絶縁化が必要となる。 ブロック膜は広いバンドギャップ(E。)と高い

ブロック膜は広いバンドギャップ( $E_g$ )と高い比誘電率を持つ $Al_2O_3$ と $SiO_2$ の積層膜が適用されている[7]。この $Al_2O_3$ の伝導帯の下端が真空準位に近づく方向に $E_g$ が拡大すれば、制御電極の仕事関数とのオフセットが高くなり、リーク電流を抑えられる。ここで、種々の $Al_2O_3$ 相の

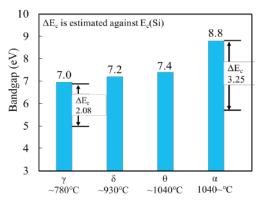

$E_g$  と Si に対する伝導帯オフセット( $\Delta E_c$ )を図 2 に示す[8-15]。先行研究によると、厚さ数 nm の  $Al_2O_3$  膜の熱的に最安定な構造は図 2 に示した全ての  $Al_2O_3$  相の中で最も  $E_g$  が狭い  $\gamma$ - $Al_2O_3$  であると報告されている[14]。 BiCS FLASH<sup>M</sup>のメモリセルの  $Al_2O_3$  膜厚も数 nm であり  $\gamma$ - $Al_2O_3$  を適用せざるを得ないのが現状である[16]。

本研究では、極薄膜の窒化アルミニウム(AIN)膜を酸化する新しいプロセスを開発し[17]、 $\gamma$ -Al<sub>2</sub>O<sub>3</sub>よりも $E_g$ の広い結晶相を持つ $Al_2$ O<sub>3</sub>薄膜の作製を試みることで更なる高絶縁化を検討した。結果として、従来の $\gamma$ -Al<sub>2</sub>O<sub>3</sub>とは異なる結晶相の、より $E_g$ の広い $\theta$ -Al<sub>2</sub>O<sub>3</sub>の実現を示唆する物理分析結果を得た。また電気特性評価からリファレンスサンプルと比較して低リーク電流密度と低固定電荷密度が実証したので報告する。

図1. 書込み/消去動作概略図

図 2. バルク Al<sub>2</sub>O<sub>3</sub> 相の相転移温度と E<sub>g</sub>

#### 2. 実験条件

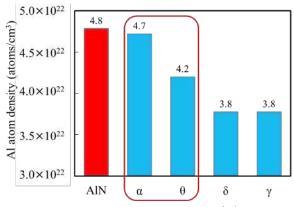

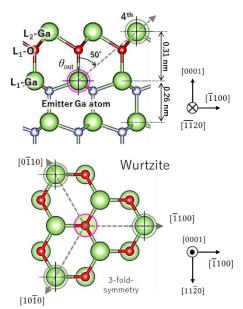

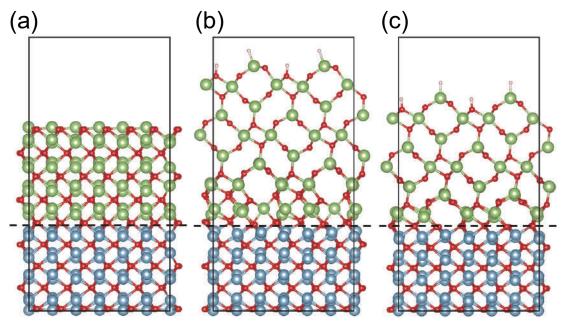

本節では、より広い  $E_g$ を有する  $Al_2O_3$ を形成するための概念について説明する。図 3 はウルツ鉱型の結晶構造の AlN と、図 2 で比較した  $Al_2O_3$  各相の Al 原子密度を示す。この図から、 $E_g$  の広い  $Al_2O_3$  相( $\alpha$  相または  $\theta$  相)と AlN の Al 原子密度の差は小さいことが確認できる[9]。ここで、Al 原子の密度が高い AlN を、その密度を維持する酸化処理によって  $\gamma$  相よりも Al 密度が高い  $\alpha$  相または  $\theta$  相の  $Al_2O_3$  が形成されるのではないかと考えた。そこで、本研究では AlN 薄膜を適切に酸化することで、 $\gamma$  相より広い  $E_g$  をもつ結晶構造の  $Al_2O_3$  薄膜を作製することを目的とした。

図 3. AlN と Al<sub>2</sub>O<sub>3</sub>の Al 原子密度

AIN薄膜を酸化することで $Al_2O_3$ 薄膜を作製するプロセスを示す。まず、Si 基板上に $SiO_2$ 薄膜を Wet 酸化法で作製した。次に、超高真空( $1\times 10^9$  Pa以下)チャンバー内で物理蒸着法(PVD)を用いて、ウルツ鉱型構造でありかつ化学量論比の AIN 薄膜(2.0 および 2.5 nm)を  $SiO_2$ /Si 基板上に作製した。この超高真空システムは、成膜装置内での AIN 膜の酸化を極力防止するために用いた。AIN 成膜後、減圧下で  $H_2$  と  $O_2$  ガスを用いて  $1000^{\circ}$ C から  $1100^{\circ}$ C の範囲で AIN の熱酸化を行った。また、リファレンスとして原子層

堆積法で形成した(ALD)- $Al_2O_3$  を用いた。AIN酸化  $Al_2O_3$  および ALD- $Al_2O_3$  の結晶構造は、透過型電子顕微鏡(TEM)像からの高速フーリエ変換法(FFT)、ナノビーム電子回折法(NBD)、面内X線回折法(In-plane XRD)を用いて評価した。更に、反射電子エネルギー損失分光法(REELS)を用いた  $E_g$  評価および原子間力顕微鏡(AFM)を用いた表面ラフネス評価を行った。また、リーク電流密度および固定電荷密度といった電気特性評価を行うため、 $W/TiN/Al_2O_3/SiO_2/p$ -Si 金属酸化物半導体キャパシタ(MOS capacitor)を作製し、容量-電圧(C-V)および電流-電圧(I-V)測定を行った。

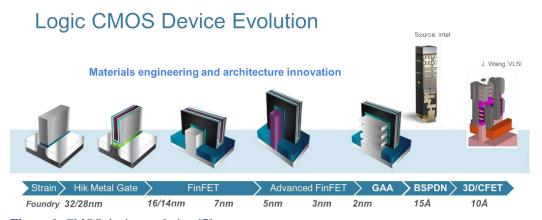

#### 3. 結果

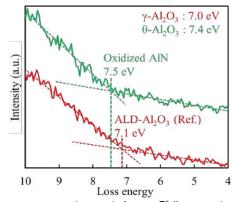

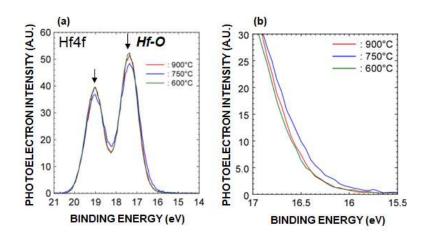

図4はALD-Al<sub>2</sub>O<sub>3</sub>(2.7 nm)とAlN酸化Al<sub>2</sub>O<sub>3</sub>(2.0 nm)のREELS スペクトルを示す。ALD-Al<sub>2</sub>O<sub>3</sub>の  $E_g$ は7.1eVであり、 $\gamma$ -Al<sub>2</sub>O<sub>3</sub>の  $E_g$ とほぼ同等であったのに対し、AlN酸化Al<sub>2</sub>O<sub>3</sub>の  $E_g$ は7.5eVと、 $\gamma$ -Al<sub>2</sub>O<sub>3</sub>よりも有意に広く、 $\theta$ -Al<sub>2</sub>O<sub>3</sub>に近いことが分かった。これらの結果から、薄膜AlN酸化Al<sub>2</sub>O<sub>3</sub>により従来の $\gamma$ -Al<sub>2</sub>O<sub>3</sub>より広い $E_g$ のAl<sub>2</sub>O<sub>3</sub> 薄膜が実現できることが明らかになった。

図 4. ALD-Al<sub>2</sub>O<sub>3</sub> (2.7 nm) と AlN 酸化 Al<sub>2</sub>O<sub>3</sub> (2.0 nm) の REELS スペクトル

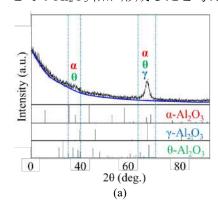

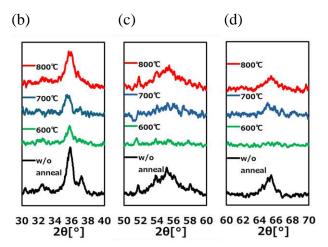

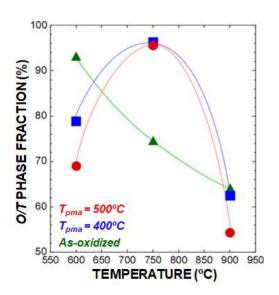

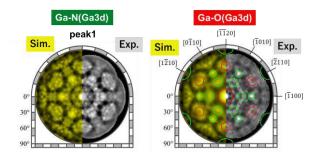

図 5(a)に AIN 酸化  $AI_2O_3$  薄膜の XRD スペクトルを示す。 $33^\circ$   $\{100\}$ 、 $36^\circ$   $\{002\}$ 、 $38^\circ$   $\{101\}$ 、 $59^\circ$   $\{2\text{-}10\}$  に出現するはずの AIN 起因の回折ピークは確認されないことから、本熱酸化手法により AIN は完全酸化されたと考える。図 5(b) に AIN 酸化  $AI_2O_3$  薄膜の NBD パターンを示す。矢印は  $\theta$ - $AI_2O_3$  [107] 方向または  $\gamma$ - $AI_2O_3$  [111] 方向からの晶帯軸入射の回折スポットと一致することを確認した。 $\theta$ - $AI_2O_3$  0[107] 方向は[001] 方向とほぼ同じである(差分: $\sim$ 4°)。ウルツ鉱型 AIN (0001)表面酸化のこれまでの実験および第一原理計算に基づく理論計算では、 $\theta$ - $AI_2O_3$  [001] 方向 AIN (0001)の両方の界面構造の候補が報告されている [15, 16]。これらの研究結果を考慮すると、1

この回折パターンは  $\theta$ -Al<sub>2</sub>O<sub>3</sub> の[107]方向入射であると推定され、バンドギャップ解析からの結果と合わせて  $\theta$ -Al<sub>2</sub>O<sub>3</sub> 相が形成したと考える。

図 5. AlN 酸化 Al<sub>2</sub>O<sub>3</sub> の(a) In-plane XRD スペクトルと(b) AlN 酸化 Al<sub>2</sub>O<sub>3</sub> の NBD パターン

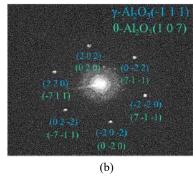

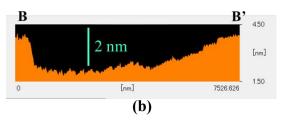

図 6(a)は低倍率で撮影した断面 TEM 像である。 この結果から、AIN 酸化 Al<sub>2</sub>O3膜は矢印で示す ように多数の結晶粒からなる。この結果から、 AlN 酸化 Al<sub>2</sub>O<sub>3</sub> 膜は多結晶構造である。図 5(b) と(c)は、AIN 酸化 Al<sub>2</sub>O<sub>3</sub>膜の断面 TEM 像とそ の FFT パターンである。垂直直線上に配置され た明瞭な点線 (図中矢印で示す) が観察され、 観察された結晶が Si 基板表面に対して垂直に 配向していることを示している。SiOっ上に成膜 した AIN 膜は、[0001]、すなわち c 軸が基板表 面に垂直な配向を持つウルツ鉱型構造になる ことが明らかにされており、本開発の AIN 薄膜 においても c 軸配向を確認している [18-20]。 この AIN の配向性が酸化処理後に形成した Al<sub>2</sub>O<sub>3</sub>においても維持されたと考える。加えて、 AIN 酸化前後において膜厚が維持されたことを 確認している。つまり AIN の AI の原子密度を 維持したまま酸化されたことで、AINの酸化工 程で付与された面内応力が酸化後も十分に解 放されず $\gamma$ -Al<sub>2</sub>O<sub>3</sub>とは異なる θ-Al<sub>2</sub>O<sub>3</sub>の形成を誘 発したと考える。面内応力の影響については後 述する。

以上の In-plane XRD、NBD、REELS、TEM による物理的特性評価の結果、AlN 酸化  $Al_2O_3$  膜は面直方向に配向し、その結晶構造は  $\theta$ - $Al_2O_3$

であることが確認された。

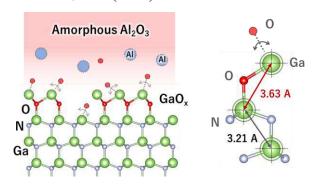

図 6. (a)低倍断面 TEM 像, (b)高倍断面 TEM 像, (c)FFT パターン

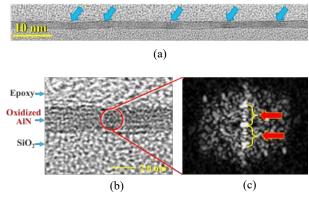

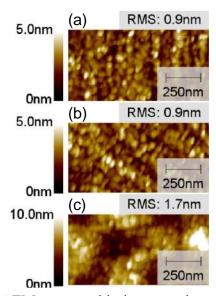

図 7 は、AIN 酸化  $Al_2O_3$  膜厚 2.0 nm (図 7(a)) と 2.5 nm (図 7(b))の表面 AFM 像である。酸化した AIN 膜の表面粗さは 2.5 nm では高さ 2.3 nm の凹凸が観察されたが、2.0 nm ではそれよりも小さかった。これは、図 3 に示すように、AIN の AI 密度( $4.8(atoms/cm^3)$ )が他の  $Al_2O_3$  結晶相に比べて高く、酸化処理時の横方向の面内応力が凹凸の形成に関与していると考える。つまりこの現象は、AIN 膜が酸化することで膨張することによる応力が 2.5nm で面直方向に解放されたのに対し、2.0nm では応力が解放されず、残留したことで高密度な  $Al_2O_3$  の結晶相である  $\theta$ - $Al_2O_3$  が発現したと考える。

図 7. AlN 酸化 Al<sub>2</sub>O<sub>3</sub> 膜厚(a)2.0 nm, (b) 2.5 nm の表面 AFM 像

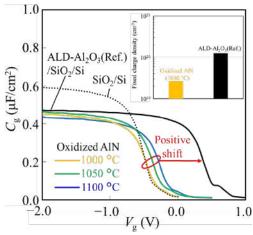

図 8 に 1 kHz における C-V 特性および C-V 特性から 算出した膜中固定電荷密度をALD-Al<sub>2</sub>O<sub>3</sub>膜と AlN 酸化 Al<sub>2</sub>O<sub>3</sub>膜で比較した結果を示す。いずれの Al<sub>2</sub>O<sub>3</sub>膜の誘電率も 9.0 であった。W/TiN/ALD-Al<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub>/p-Si キャパシタのフラットバンド電圧( $V_{tb}$ )は、W/TiN/SiO<sub>2</sub>/p-Si キャパシタと比較して正バイアス側にシフトした。正の  $V_{tb}$ シフトは、 $\gamma$ -Al<sub>2</sub>O<sub>3</sub>の 4 配位 Al<sup>3+</sup>イオンが Al<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub>界面の酸素マイグレーションに起因する。その結果、ダイポールが正の  $V_{tb}$ シフトを誘起すると考えられている [21-24]。今回、正の  $V_{tb}$  シフトが抑制された理由は結晶

構造の変化に加えて高配向 の Al<sub>2</sub>O<sub>3</sub> によって この界面での酸素の移動が阻害され、ダイポー ルの形成が妨げられたのではないかと考える。 V<sub>b</sub>シフト量から固定電荷密度を比較した結果 を図 8 の挿入図に示した。この固定電荷密度は、 Al<sub>2</sub>O<sub>3</sub> 膜中の電荷分布が均一であると仮定した 場合の式(1)を用いて計算したものである。

$$N = (2\varepsilon \varepsilon_o \Delta V_{fb})/qx^2$$

(1)

ここで、Nは固定電荷密度、εはAl<sub>2</sub>O<sub>3</sub>の比誘 電率、&は真空中の誘電率、xはAl<sub>2</sub>O<sub>3</sub>膜厚、q は電荷量である。固定電荷密度は、従来の ALD-Al<sub>2</sub>O<sub>3</sub>よりも AIN 酸化 Al<sub>2</sub>O<sub>3</sub>の方が約1桁 低かった。ALD-Al<sub>2</sub>O<sub>3</sub>の結果は、Al<sub>2</sub>O<sub>3</sub>膜中の4 配位 Al3+によって誘起された負の固定電荷に起 因すると考えられる[25]。一方, W/TiN/AIN 酸 化 Al<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub>/p-Si キャパシタでの V<sub>fb</sub>値は,酸 化温度にかかわらず W/TiN/SiO<sub>2</sub>/p-Si キャパシ タと同程度であった。これは、AIN 酸化 Al<sub>2</sub>O<sub>3</sub> が負の固定電荷の形成を抑制していることを 示している。γ-Al<sub>2</sub>O<sub>3</sub>の場合、欠陥スピネル構造 に由来する4配位 Al3+の存在による負の固定電 荷は避けられない。AIN酸化 Al2O3でも高温酸 化ほど Vnが正のバイアス側にシフトするのは、 膜質劣化に起因して負の固定電荷が発生する ためと考えられるが、 $ALD-Al_2O_3$  ほどには  $V_{fb}$ はシフトしていない。更に、AIN 酸化 Al<sub>2</sub>O<sub>3</sub>で は、TEM と In-plane XRD による構造解析で大 きな変化は観察されなかった。これらの結果は AIN酸化Al<sub>2</sub>O<sub>3</sub>がγ-Al<sub>2</sub>O<sub>3</sub>とは本質的に異なるこ とを裏付けている。固定電荷に加えて、ダイポ ールも V<sub>f</sub> シフトさせるもう一つの要因である。 重要な要因が固定電荷かダイポールかについ ては、Al<sub>2</sub>O<sub>3</sub>や SiO<sub>2</sub>の膜厚に対する V<sub>fb</sub>依存性 を詳細に調べ、今後明らかにする予定である。

図 8. Al<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub>/p-Si キャパシタの C-V 特性

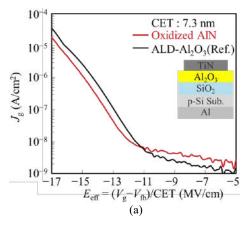

図 9(a)に、AIN 酸化 Al<sub>2</sub>O<sub>3</sub> と ALD-Al<sub>2</sub>O<sub>3</sub> のリーク電流密度(J<sub>g</sub>)を比較した結果を示す。CET は容量換算膜厚(capacitance equivalent thickness)

を表す。AIN 酸化 Al<sub>2</sub>O3の Jg は、高実効電界(Eeff) 領域(>11 MV/cm)において、ALD-Al<sub>2</sub>O<sub>3</sub> よりも 低いことがわかる。γ-Al<sub>2</sub>O<sub>3</sub>と TiN 電極間の電子 障壁は 2.7 eV である。AIN 酸化 Al<sub>2</sub>O<sub>3</sub> ではリー ク電流が減少しているため、Egの増大が ΔEcを に反映されたと考える。一方、低 Eeff 領域(<11 MV/cm)におけるリーク電流は、ALD-Al2O3より も AIN 酸化 Al<sub>2</sub>O<sub>3</sub>の方が大きかった。図示して はいないが、I-V ヒステリシス特性において同 電界領域では負の電流を示していることから、 キャパシタを貫通する電流ではなく充電電流 が主成分であることを確認している。この過渡 応答電流が増加する理由は不明だが、今後周波 数依存性や電流―時間依存性等によってキャ パシタの誘電緩和の詳細な解析を試みる予定 である。

図 9 (b)は、AIN 酸化 Al<sub>2</sub>O<sub>3</sub> におけるリーク電 流密度の温度依存性を示している。測定は同じ キャパシタを用い、14 MV/cm の実効電界で評 価した。また、測定温度は 27~125℃の温度範 囲で行った。リーク電流密度は、温度が27℃か ら上昇するにつれて通常の Al<sub>2</sub>O<sub>3</sub> では減少傾向 になるが、AIN 酸化 Al<sub>2</sub>O<sub>3</sub> ではほとんど変化し なかった。この結果から、AIN 酸化 Al<sub>2</sub>O<sub>3</sub>のリ 一ク電流密度は温度依存性が非常に小さいこ とが確認された。したがって、リーク電流メカ ニズムは、浅いトラップを経由する Poole-Frenkel(PF) 電流ではなく Fowler-Nordheim(FN)電流またはトラップアシ ストトンネル(TAT)電流のようなトンネル電流 由来のリーク電流である可能性が高いと考え る。このリークメカニズムは、結晶性の向上、 固定電荷の減少、Egの拡大(主に ΔEc)による欠 陥準位の深化、によって説明可能で、AIN 酸化  $Al_2O_3$  では欠陥が抑制されていることを示唆し ている。今後、この絶縁特性を向上させるメカ ニズムについては、硬X線光電子分光等の物理 解析やバンドアライメント解析、リークシミュ レーション等を行う予定である。

以上の結果から AIN 薄膜を酸化することによって、低リーク電流と低固定電荷密度を両立することを示した。

図 9. (a)Jg と Eeff、(b)Jg 酸化 AlN の温度依存性

#### 4. まとめ

c 軸配向した AIN 薄膜を酸化処理することによって、薄膜において熱的に安定な  $\gamma$ -Al<sub>2</sub>O<sub>3</sub> 比べて  $E_g$  が広い  $\theta$ -Al<sub>2</sub>O<sub>3</sub> 薄膜を実現した。 $\theta$ -Al<sub>2</sub>O<sub>3</sub> の形成は、AIN 薄膜の配向性を酸化後でも維持している Al<sub>2</sub>O<sub>3</sub> の残留応力に起因すると考える。また、キャパシタ特性から AIN 酸化 Al<sub>2</sub>O<sub>3</sub> は従来の ALD-Al<sub>2</sub>O<sub>3</sub> と比較して固定電荷を抑制できることに加え、リーク電流を低減できることを明らかにした。本研究で開発されたプロセスを適用した Al<sub>2</sub>O<sub>3</sub> をブロック膜に適用するにより、3D フラッシュメモリの消去動作性能の向上が期待できると考える。

このプロジェクトは、3Dフラッシュメモリの 共同開発に関して、ウエスタンデジタル社とキ オクシア社から支援を受けている。

- [1] S. Chen, Y. Chang, Y. Liang, H. Wei and W. Shin, IEEE Trans. Comput., **67**, 9 (2018).

- [2] H. Tanaka, M. Kido, K. Yahashi, M. Oomura, R. Katsumata, M. Kito, Y. Fukuzumi, M. Sato, Y. Nagata, Y. Matsuoka, Y. Iwata, H. Aochi and A. Nitayama, Symp. on VLSI Tech. Dig., 14 (2007).

- [3] A. Nitayama and H. Aochi, ECS Trans., **41**, 15 (2011).

- [4] Micheloni, R. (Ed.) 3D Flash Memories, Springer: Berlin (2016).

- [5] J. Wu, et al., IEEE J. Electron Devices Soc., ver.7 (2019).

- [6] Doo-Hyun Kim et al., Jpn. J. Appl. Phys. **49**, 084301 (2010).

- [7] G. Hemink and A. Goda, in Semiconductor Memories and Systems. (Eds A. Redaelli, F. Pellizzer), Woodhead Publishing, 119–158 (2022).

- [8] S. Miyazaki, J. Vac. Sci. Technol. B, 19, 2212 (2001).

- [9] K. Wefers and C. Misra, Alcoa Technical Paper, no. 19, Revised Alcoa Laboratories (1987).

- [10] M. Digne, P. Sautet, P. Raybaud, H. Toulhoat and E. Artacho J. Phys. Chem. B **106**, 5155 (2002).

- [11] M. F. Peintinger, M. J. Kratz and T. Bredow, J. Mater. Chem. A, **2**, 13143 (2014).

- [12] R. Franchy, Surf. Sci. Rep., 38, 195 (2000).

- [13] J. Robertson, Rep. Prog. Phys., 69, 327 (2006).

- [14] J. M. McHale, A. Auroux, A. J. Perrotta and A. Navrotsky, Science, **277**, 788 (1997).

- [15] Z. Fang, E. Wang, Y. Chen, X. Hou, K. C. Chou, W. Yang, J. Chen and M. Shang, ACS Appl. Mater. Interfaces, 10, 30811 (2018).

- [16] J. H. Dycus, K. J. Mirrielees, E. D. Grimley, R. Kirste, S. Mita, Z. Sitar, R. Collazo, D. L. Irving and J. M. LeBeau, ACS Appl. Mater. Interfaces, 10, 10607 (2018).

- [17] Y. Nakajima, A. Takashima, M. Noguchi, T. Isogai, "Reducing Leakage Current with Wider-Bandgap Alumina Films Formed by Ultrathin-AlN Oxidation", 2023 International Conference on Solid State Devices and Materials, E-6-04.

- [18] A. Artieda and P. Muralt, IEEE Trans. Ultrason. Ferroelectr. Freq. Control **55**, 2463 (2008).

- [19] F. Engelmark, G. F. Iriarte, I. V. Katardjiev, M. Ottoson, P. Muralt, and S. Berg, J. Vac. Sci. Technol. A 19, 2664 (2001).

- [20] A. Rodríguez-Navarro, W. Otaño-Rivera, L. J. Pilione, R. Messier, and J. M. García-Ruiz, J. Vac. Sci. Technol. A **16**, 1244 (1998).

- [21] Y. Kamimuta, K. Iwamoto, Y. Nunoshige, A. Hirano, W. Mizubayashi, Y. Watanabe, S. Migita, A. Ogawa, H. Ota, T. Nabatame and A. Toriumi, IEEE Int. Electron. Device Meeting, 342 (2007).

- [22] T. Nabatame, A. Ohi, T. Chikyo, M. Kimura, H. Yamada and T. Ohishi, J. Vac. Sci. Technol., **32**, 03D121 (2014).

- [23] K. Kita and A. Toriumi, Appl. Phys. Lett. 94, 132902(2009).

- [24] A. Toriumi and T. Nabatame, High Permittivity Gate Dielectric Materials. (Ed. S. Kar), 263 (2013).

- [25] K. Torii, Y. Shimamoto, S. Saito, O. Tonomura, M. Hiratani, Y. Manabe, M. Caymax and J. W. Maes, 2002 Symposium on VLSI Technology. Digest of Technical Papers, Honolulu, HI, USA, 188 (2022).

# **Advanced Logic Transistor Process Technology Towards 1-nm Node**

Naomi Yoshida

Applied Materials Inc., Santa Clara, California, U.S.A. naomi\_yoshida@amat.com

#### **Abstract:**

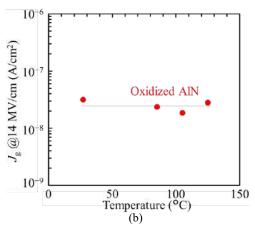

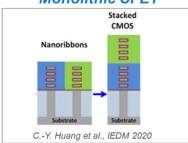

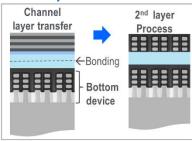

After several generations of FinFET scaling to the latest 3-nm node [1], advanced logic transistor architecture continues to evolve to horizontal gate-all-around (GAA) FET with vertically stacked Si nanosheet (NS) channel [2,3] (**Fig. 1**) [7]. Multiple innovations of process technology are required for NS-GAA implementation in high volume manufacturing (**Fig. 2**) [8]. Beyond NS-GAA and other scaling boosters such as backside power delivery, novel transistor architectures are in the pipeline for future CMOS scaling. One of the proposed new architectures is to vertically stack PMOS and NMOS, also known as CFET, for effective CMOS area scaling. CFET fabrication is proposed in mainly two different integration approaches (**Fig. 3**), sequential and monolithic integration [4-6].

This presentation describes process challenges and process technology solutions for GAAFETs as the next transistor inflection <sup>[7]</sup>. In addition, we'll discuss the next scaling inflections such as backside power delivery BS-PDN and CFET process integration options.

Figure 1. CMOS device evolution [7]

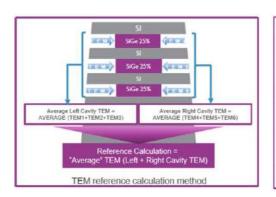

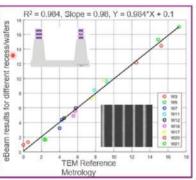

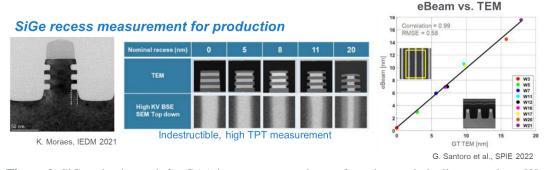

Figure 2. SiGe selective etch for GAA inner spacers and manufacturing ready in-line metrology [8]

#### **Monolithic CFET**

Top and Bottom channel formation together

#### Sequential CFET

- Bottom MOSFET (N or P)

- 2<sup>nd</sup> channel blanket layer

- Top MOSFET (P or N) formation

## **Self-aligned patterning**

# Simplified processing (of each layer)

**Figure** 3. Two approaches of CFET [7,9,10]

- [1] S-.Y. Wu et al., "A 3nm CMOS FinFlexTM Platform Technology with Enhanced Power Efficiency and Performance for Mobile SoC and High Performance Computing Applications," 2022 IEDM, pp. 639-641.

- [2] H. Mertens et al., "Vertically Stacked Gate-All-Around Si Nanowire CMOS Transistors with Reduced Vertical Nanowires Separation, New Work Function Metal Gate Solutions, and DC/AC Performance Optimization," 2017 IEDM, pp. 508-511.

- [3] N. Loubet et al., "Stacked Nanosheet Gate-All-Around Transistor to Enable Scaling Beyond FinFET," 2017 VLSI Technology, pp. 230-231.

- [4] J. Ryckaert et al., "The Complementary FET (CFET) for CMOS scaling beyond N3," 2018 VLSI Technology, pp. 141-142.

- [5] S. Subramanian et al., "First Monolithic Integration of 3D Complementary FET (CFET) on 300mm Wafers", 2020 VLSI Technology, pp. 1-2

- [6] R. Chau, "Process and Packaging Innovations for Moore's Law Continuation and Beyond," 2019 IEDM, pp. 1-5.

- [7] N. Yoshida, "Advanced Logic Transistor Process Technology Towards 1-nm Node", 2023 VLSI-T Short Course

- [8] G. Santoro et al., "Recess metrology challenges for 3D device architectures in advanced technology nodes," 2022 SPIE, Vol. 12053, pp. L1-13

- [9] C-.Y. Huang et al., "3-D Self-aligned Stacked NMOS-on-PMOS Nanoribbon Transistors for Continued Moore's Law Scaling," 2020 IEDM, pp. 425-428.

# シリコン量子ビットデバイスの特性における界面の影響

# Impact of interfaces on characteristics of silicon spin qubits

小林 嵩

理化学研究所量子コンピュータ研究センター 〒351-0198 埼玉県和光市広沢 2-1 Takashi Kobayashi

RIKEN Center for Quantum Computing, Wako, Saitama 351-0198, Japan e-mail:takashi.kobayashi@riken.jp

#### **Abstract**

Characteristics of silicon spin qubits are strongly influenced by the fabrication process and quality of interfaces in device. Here, we overview interfaces of spin qubits based on Si/SiGe quantum dots and their impact on the qubit characteristics. Recent development of device fabrication and device characterization technologies will be introduced.

#### 1. はじめに

量子コンピュータは量子力学の原理を応用 した情報処理装置である。従来のコンピュータ では計算が困難な問題を解くことができる可 能性があることから、近年研究・開発が盛んに 行われている。量子コンピュータでは処理され るデータを量子ビットと呼ばれる2準位系の量 子状態を用いて表現する。量子ビットとして利 用できる物理系のひとつとして、シリコン中の スピン自由度が挙げられる。このタイプの量子 ビットは、既存の半導体製造技術との親和性が 高いことや比較的に高い温度で動作しうるこ とから注目されている。近年、少数の量子ビッ トからなるデバイスで誤り耐性閾値を超える ゲート忠実度[1]や位相誤り訂正[2]が実現され、 量子コンピュータを実現する上での有用性が 認識されてきている。しかしながら、大規模な 量子コンピュータを実現する上では量子ビッ トデバイスの特性をさらに向上させることが 必要である。

#### 2. 量子ビットデバイスの特性

量子ビット自体は各種の操作に対する忠実度によって特徴づけられる。一方で、量子ビットを実装するためのデバイスはアナログな実体であり、様々な物理的特性によって特徴づけられる。シリコン量子ビットデバイスの場合に

操作忠実度に関係するデバイスの特性の一例 を挙げる:

- ノイズスペクトル密度

- 谷分離の大きさ

また、量子コンピュータの実現に必要な大規模な量子ビット列においては、閾値電圧の一様性も重要となると考えられる。これらのデバイス特性は界面から強い影響を受けることが知られており、良い特性を得られる界面の作り方が検討されてきた。

#### 3. 界面の特性とその評価方法

本講演では、主として Si/SiGe 量子井戸から 作製されるスピン量子ビットデバイスの界面 に関する研究を紹介する。この型の量子ビット デバイスにおいては、磁気的なノイズと谷分離 の大きさに影響する量子井戸と、電気的なノイ ズと閾値電圧の一様性に関係する半導体基板 の表面が重要な界面である。

量子井戸においては、磁気的なノイズの源である核スピンを減らすために同位体制御が標準的に行われるようになっている。また、大きな谷分離を得られるように原子ステップ密度の低減や、薄い量子井戸の採用、さらにはスパイク状のゲルマニウム層の導入などの構造的工夫が考案されている。

半導体基板表面ではゲート構造を作りつける際の基板へのダメージに由来する欠陥や、ゲート絶縁膜に由来する固定電荷の影響で閾値電圧にばらつきが生じる。また同時に電気的なノイズの源ともなりうることから、製造工程の

最適化によりこれらの密度を制御することが 肝要である。近年、製造工程の最適化により閾 値電圧の均一性の向上が実現できることが報 告されている[3]。

シリコン量子ビットデバイスの特性は既存の製造技術あるいはその拡張によって向上できる可能性がある。しかしながら、量子ビットデバイスの評価には低温での測定が必須難とるため、製造工程へのフィードバックが困難となっている。近年では低温プローバーによって関値電圧をウェハスケールで短時間の内によって関値電圧をウェクルで短いイスを同時に評価する、あるいは極低温マルチプレクサにより複数の量子ビットデバイスを同時に評価できなどのアプローチが取られるようになってなっていては今後さらなる発展が待たれている。

#### 4. 謝辞

本研究は、科学技術振興機構ムーンショット型研究開発事業目標6の研究開発プロジェクト「拡張性のあるシリコン量子コンピュータ技術の開発(No. JPMJMS226B、プロジェクトマネージャー: 樽茶清悟) および日本学術振興会科学研究費助成事業(No. 22H01160) による助成を受けて行われた。

- [1] A. Noiri et al., Nature 601, 308-342 (2022).

- [2] K. Takeda et al., Nature 608, 682-686 (2022).

- [3] S. Neyens *et al.*, Nature **608**, 682-686 (2022).

# シリコン量子ビット技術と集積化に向けた研究開発

# Research and development towards silicon qubit technology and integration

小寺 哲夫

東京工業大学 〒152-8552 東京都目黒区大岡山 2-12-1 S3-25 Tetsuo Kodera

Tokyo Institute of Technology, S3-25, 2-12-1 Ookayama, Meguro, Tokyo 152-8552, Japan Tel:+ 81-3-5734-3421, Fax: + 81-3-5734-3421 (e-mail:kodera.t.ac@m.titech.ac.jp)

#### **Abstract**

It is expected that mature semiconductor integration technology will be utilized in quantum computers. In particular, research into quantum bits that utilize spins in semiconductor quantum dots is being actively pursued from the viewpoint of coherence and compatibility with electronics technology. Research and development is also progressing on electronics for controlling qubits that operate at low temperatures and on peripheral technologies for large-scale integration of qubits. In this talk, I will discuss the trends, challenges, and prospects of research and development of spin qubits, as well as the current status of our research.

#### 1. はじめに

超伝導をはじめとするさまざまな物理系において、量子コンピュータハードウェアに向けた研究開発が盛んに行われている[1,2]。半導体系での研究開発も活発になっている。半導体集積技術は成熟しており、量子コンピュータへの応用が期待される。

半導体量子ビット研究は、以前は主に GaAs 量子ドット内の電子スピンを利用して、物理の探究と基礎技術の開発に焦点が当てられていた[3-6]。しかし、成熟してもなお成長著しいシリコン集積技術との融合やデコヒーレンスの問題を考慮した結果、シリコン系での量子ビット技術と集積化を中心に研究開発が展開している状況である[7]。

## 2. シリコンスピン量子ビット研究

シリコン系での研究は、この 10 年間で目覚ましい進歩を遂げている。スピン量子ビット研究の重要なステップとして、単一電子状態の実現、スピンブロッケード現象の観察、スピンのシングルショット読み出し[8]、スピン操作[9-12]、および 2 量子ビット操作[13]が実現され

てきた。また集積化に関わる研究として、長距離スピン結合のための光子結合[14,15]、およびスピン量子ビットの高温動作[16,17]も実現されている。最近では、量子もつれ状態が観察され[18]、量子誤り訂正の原理実証が 3 量子ビットで行われ[19]、6 量子ビットの動作も実現した[20]。2023 年には、Intelが Tunnel Falls と呼ばれる 12 量子ビットデバイスをさまざまな研究機関に配布し、研究開発がますます加速すると期待される。

量子ビットの大規模集積に向けて、世界中の 企業、研究機関、大学が連携している。アーキ テクチャ、配線、クライオエレクトロニクスな ど、周辺技術も含めてさまざまな研究開発が進 んでいる。

#### 3. 研究進捗

東工大では、シリコン量子ビットに向けて、MOS トランジスタ構造を利用して物理的に形成したシリコン量子ドットを作製し研究してきた[21-30]。単一電子状態の電荷検出[23]、スピンブロッケード状態の実現[21]、多重量子ドット特性の観測を行ってきた[25]。また、単一電子トンネリングのシングルショット読み出し[27]や RF 単一電子トランジスタ[29]も実現した。p

チャネルシリコン量子ドットでは、単正孔状態 [22]、スピンブロッケード状態[24]、高温での単正孔輸送[26]、および正孔スピン共鳴を実現した。MOS 構造をベースとして物理的に形成した量子ドット構造はシリコン技術を使用して作製できるため、将来の量子ビットの集積化に適していると期待されている。近年は、産業技術総合研究所との共同研究で素子作製を行っており、安定的なデバイス動作に向けて、界面等における電荷トラップやラフネスの低減への取り組みを進めている。

また、日立製作所との共同研究においては、MOS 構造をベースとしたシリコン量子ドットアレイを開発した[31]。シリコン集積回路技術を量子ビット制御に直接利用することを目的として、量子ドットアレイを制御する量子ビットチップ上に CMOS 回路を集積する実験について報告した[32]。さらに、単一電子を量子ドットアレイにロードするための技術として単一電子ポンプも実証した[33]。

Si/SiGe ヘテロ構造を用いた量子ドットでは、理化学研究所との共同研究により単一量子ビット動作を実現した[34]。さらに、近年では、99.9%を超える高忠実度の単一量子ビット操作[35]や非破壊量子計測[36]などの重要な要素技術を開発し、二次元量子ドットアレイの設計提案[37]を行っている。

#### 4. まとめ

成熟した半導体集積技術が量子コンピュータに活用されることが期待されている。特に、シリコン系量子ドットのスピンを利用した量子ビットの研究は、コヒーレンスやエレクトロニクス技術との親和性の観点から盛んに進められている。また、極低温で動作する量子ビットを制御するためのエレクトロニクスや量子ビットの大規模集積化のための周辺技術の研究開発も進められている。我々も企業、研究機関と連携して、研究開発を進めている。

本研究は、JST Moonshot R&D (JPMJMS2065), MEXT QLEAP (JPMXS0118069228), 科学研究費 補助金 (JP23H05455, JP23K17327)によってサ ポートされた。

- [1] M.W. Johnson, et al., Nature 473, 194 (2011).

- [2] Y. Nakamura, et al., Nature 398, 786 (1999).

- [3] K. Ono, et al., Science 297, 1313 (2002).

- [4] J. R. Petta, et al., Science 309, 2180 (2005).

- [5] F. H. L. Koppens, et al., Nature 442, 766 (2006).

- [6] T. Kodera, et al., Phys. Rev. Lett. 102, 146802 (2009).

- [7] K. M. Itoh and H. Watanabe, Mater. Res. Soc. Commun. 4, 143 (2014).

- [8] A. Morello, et al., Nature 467, 687 (2010).

- [9] E. Kawakami, et al., Nat. Nanotechnol. 9, 666 (2014).

- [10] B. M. Maune, et al., Nature 481, 344 (2012).

- [11] M. Veldhorst, et al., Nat. Nanotechnol. 9, 981 (2014).

- [12] M. Veldhorst, et al., Nature 526, 410 (2015).

- [13] T. F. Watson, et al., Nature 555, 633 (2018).

- [14] N. Samkharadze, et al., Science 359, 1123 (2018).

- [15] X. Mi, et al. Nature 555, 599 (2018).

- [16] L. Petit, et al. Nature 580, 355 (2020).

- [17] C. H. Yang, et al. Nature 580, 350 (2020).

- [18] K. Takeda, et al.: Nat. Nanotechnol. 16, 965 (2021).

- [19] K. Takeda, et al., Nature 608, 682 (2022).

- [20] S.G.J. Philips, et al., Nature 609, 919 (2022).

- [21] G. Yamahata, TK, et al. Phys. Rev. B 86, 115322 (2012).

- [22] K. Yamada, TK, et al., Appl. Phys. Lett. 105, 113110 (2014).

- [23] K. Horibe, TK, et al., Appl. Phys. Lett. 106, 083111 (2015).

- [24] Y. Yamaoka, TK, et al., Jpn. J. Appl. Phys. 56, 04CK07 (2017).

- [25] R. Mizokuchi, TK, et al., Appl. Phys. Lett. 114, 073104 (2019).

- [26] N. Shimatani, TK, et al., Appl. Phys. Lett. 117, 094001 (2020).

- [27] R. Mizokuchi, TK, et al., Appl. Phys. Express 13, 121004 (2020).

- [28] S. Bugu, TK, et al., Sci. Rep. 11, 20039 (2021).

- [29] R. Mizokuchi, TK, et al., Sci. Rep., 11, 5863 (2021).

- [30] S. Nishiyama, TK, et al., Sci. Rep. 12, 10444 (2022).

- [31] N. Lee, TK, et al., Appl. Phys. Lett. 116, 162106 (2020).

- [32] N. Lee, TK, et al., Jpn. J. Appl. Phys. 61, SC1040 (2022).

- [33] T. Utsugi, TK, et al., Jpn. J. Appl. Phys. 62, SC1020 (2023).

- [34] K. Takeda, TK, et al., Sci. Adv. 2, e1600694 (2016).

- [35] J. Yoneda, TK, et al., Nat. Nanotechnol. 13, 102 (2018).

- [36] J. Yoneda, TK, et al., Nat. Commun. 11, 1144 (2020).

- [37] M. Tadokoro, TK, et al., Sci. Rep. 11, 19406 (2021)

# 金属酸化物および Li イオンを用いた不揮発素子と 脳型リザバーコンピューティング等への応用

# Non-volatile devices using metal-oxide and Li ion and their applications to neuromorphic reservoir computing

丸亀 孝生 水島 公一 野村 久美子 西 義史

株式会社東芝 研究開発センター 〒212-8582 川崎市幸区東芝町 1 Takao Marukame, Koichi Mizushima, Kumiko Nomura, Yoshifumi Nishi R&D Center, TOSHIBA Corporation, 1 Komukai-Toshiba-cho, Saiwai-ku, Kawasaki 212-8582, Japan Tel:+81-50-3190-9141 (e-mail: takao.marukame@toshiba.co.jp)

#### **Abstract**

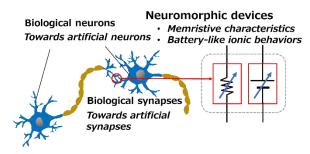

Neuromorphic AI integrated circuits use novel devices with memory mechanisms such as ferroelectricity, charge trapping, and oxygen vacancies. We have investigated metal oxide-based memory devices and explored their application as weight synapses in neural networks (NNs). First, memristive devices based on TiN/MgO/WO<sub>x</sub> thin films exhibit analog conductance properties similar to biological synapses, namely spike timing-dependent plasticity has been observed. These memristive devices can be applied to low-power analog neuron circuits. Second, TiN/MgO/Si devices, which combine low-current operation and diode characteristics, can further reduce the power consumption of circuits, and can be used for time-series NN signal processing in array configurations. Recently, ionic-electronic hybrid material systems have attracted further attention to expand the range of neuromorphic applications. Among ionic materials, lithium (Li)-ionic materials such as LiCoO<sub>2</sub> in lithium-ion batteries and Li<sub>3</sub>PO<sub>4</sub>-N (LiPON) in all solid-state thin-film batteries are already in use. LiCoO<sub>2</sub>/LiPON devices exhibit multi-level resistance changes and are promising for analog NN circuits for in-memory computing. With multiple physical and chemical mechanisms, these devices have great potential to create a new paradigm and era of neuromorphic AI computing.

## 1. はじめに

高大規模ニューラルネットワーク (Neural Network; NN) は、深層学習や生成系などの応用で有用な人工知能 (Artificial Intelligence; AI) の基盤技術として成功を収めている。高性能なNN ベース AI を実現するためにはニューロンのシナプスに相当する大量の重み値を学習により最適化する必要がある。学習では事前の訓練に用いる学習データを積和演算処理して、出力が目的に近づくように重みを繰り返し更新する。大規模 NN の学習は大量データを扱うのに適したクラウドコンピューティングサーバや、ベクトル演算および積和演算が高速な汎用GPU (Graphic Processing Unit) を用いて実行されるのが一般的である。しかしそれでも学習処

理にかかる時間は長く大きな消費電力を必要 とすることから、学習に必要なエネルギーは膨 大となってしまう. 従って学習システムの小型 化は今のところ原理的に難しい課題であって, IoT (Internet-of-Things) 機器などがスタンドア ローンで学習するという事例は多くはない. 実 用的な現実解として, 学習は予め済ませておき, 推論用には CPU に GPU を組み合わせて用いら れ, さらに高性能な推論器が必要となる場合は ASIC (Application Specific Integrated Circuit) や SoC (System-on-Chip) が開発される. CPU, GPU, ASIC, SoC は基本的に CMOS デジタル回路で あり, 高性能化のためには高価な半導体製造プ ロセスを用いる必要がある. 今後, 推論におい て低消費電力での常時動作を可能にする AI チ ップを実現すること,加えて,学習を高効率化

して小型システムに実装するには従来型の CMOS デジタル回路よりも優れたアーキテクチャおよび新しい演算・記憶原理の導入が望まれる. その有望なアプローチの一つが脳模倣型のハードウェア技術すなわちニューロモーフィック技術である[1]-[10].

本稿では Fig.1 のようなニューロモルフィック技術において特に金属酸化物系薄膜技術を用いてシナプスを模倣した素子(以下、シナプス素子)を示す。これは不揮発メモリ素子の研究開発から派生した技術であって可変抵抗器型のいわゆるメモリスティブ (memory + resistive) な素子である。さらに最近注目を集めているイオン伝導を用いた電池型/抵抗型のハイブリッド素子の例も説明する。これらシナプス素子のニューラルネット回路に応用した際の有望性と展望も紹介する.

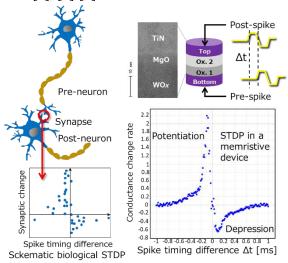

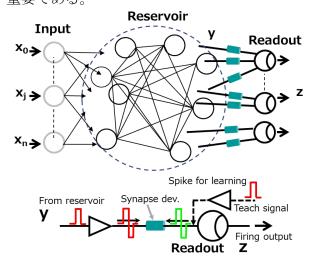

Fig.1 Schematic illustration of neurons and neuromorphic devices

#### 2. 脳神経を模倣した抵抗変化素子

脳の中のシナプスの記憶と学習に関する可塑性と呼ばれる仕組みでは、入出力の電圧信号により強度が変化し、その増減はそれら電圧信号の時間差により決定されるという Spike-Timing Dependent Plasticity (STDP) が知られている。金属酸化物素子はメモリスティブな特性を示すことが知られており、そのうち $WO_x/W$ 素子の STDP 模倣が早くから報告されていた。また STDP の原理を NN の学習器に取り込むことによるオンライン学習などの自律型学習器の可能性が提案されていた。

不揮発メモリ素子に関する代表的な金属酸化物型の AlO<sub>x</sub>/TiO<sub>x</sub> 2 層を抵抗変化層に用いた素子においても電圧印加によるメモリスティブな特性が観測され、その抵抗変化にて STDP 特性を観測可能であった[2]. この構造にさらにMgO をトンネル障壁層として挿入することで

抵抗変化率が大きくなることが見出されていた。そこで著者らのグループは CMOS プロセス 適合性を考慮して新たに TiN/MgO/WO $_x$  型の素子を製作したところ、得られた電流電圧 (I-V) 特性にて抵抗変化幅の増加が得られ、かつ、Fig. 2 のようにアナログ微小量の変化を STDP のパルス電圧波形で制御可能なことが明らかとなった[3]、[6]-[8].

Fig.2 Spike-timing dependent plasticity (STDP) characteristics in TiN/MgO/WO<sub>x</sub> memristive device.

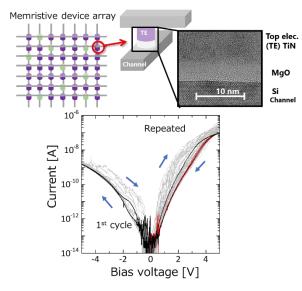

Fig.3 A memristive device of TiN/MgO/Si in an array structure and its *I-V* characteristics.

メモリスティブ素子をクロスバーやクロスポイントのアレイ構造とすることによる NN の積和演算器の高密度集積が提案されていた.強誘電体トンネル接合のアレイ構造による高効率な積和演算原理が報告された[1]. また強誘電

体トンネル接合をクロスバー上で効率的に書 き換えることによる強化学習への応用も示さ れている[9],[10]. これらのようなアレイ構造を さらに大規模化するためには、アナログ電流を 演算原理に用いるためアレイ構造中の素子間 リーク電流を抑制するための整流性が重要で ある. 著者らのグループでは抵抗変化型の *I-V* 特性にダイオード整流性を加える目的で TiN/MgO/Si 薄膜積層構造のメモリスティブ素 子を開発した(Fig.3)[11]. 正電圧において電 流が 100 nA 程度得られるのに対して負電圧で は 1 nA 程度に電流が抑えられ、明瞭な整流性 が確認できた. 正側の動作電圧領域では電流が ほぼ線形に変化し電流履歴において可塑性を 確認できた. 32×32 のアレイ構造において 個々の素子に備わるダイオード効果により, れぞれのデバイス特性を独立に読み出すこと ができる. アレイ中の2つの素子ペアをシナプ ス重みとしてそれらの動作電流を電圧変換す ることでコンパレータを介して出力させ,出力 を再帰的に入力することで順次処理できる.シ ミュレーションおよび実験の結果から、状態遷 移マップを得ることができ、これを原理とする 時系列データ処理が期待できる[11]. 以上のよ うに整流性の付与によりメモリスティブな素 子に新たな機能性を加えることができる.

# 3. Li イオンを用いた不揮発素子とリザバーコンピューティング等への応用

抵抗変化素子の材料としては、電荷トラップ 材料、相変化カルコゲナイド材料、強誘電体材 料、酸素欠損酸化物絶縁体などが知られている が、最近さらにイオン伝導系が注目されている. 最も成功しているイオン伝導性材料のひとつ は電池用途で成功しているリチウム (Li) イオ ン材料である. LiCoO<sub>2</sub>は, Li イオンを供給する Li イオン電池の正極材料として広く使用され ている. リチウムイオンを用いた全固体電池お よびその応用技術は、エレクトロニクスの新た な自由度として注目を集めている. Li イオン伝 導によるメモリスティブな素子を作製するた めに、Liイオンの流れやすさと電子の流れにく さを制御する必要があり薄膜の固体電解質は その重要な材料である. Li<sub>2</sub>PO<sub>4</sub>酸化物系での典 型的な固体電解質であり、イオン伝導特性を上 げるためにその窒化物の LiPON を用いた LiCoO<sub>2</sub>/LiPON/Cu 構造は, 薄膜全固体電池とし て機能することが知られている. これら Li イオ ン系の材料を用いて多端子のデバイスを作成 すると Li イオンの移動により導電チャネルが 抵抗変化することが報告されている. これらの 結果によると,イオン伝導は長期記憶と書き換 え信号に対する線形な抵抗変化を得るための 有望なメカニズムとなり得ることが実証され

ている.

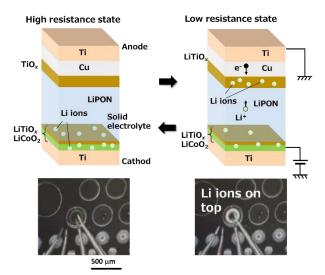

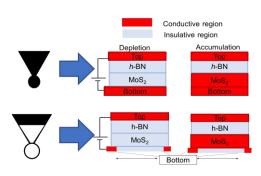

本稿では我々が最近開発した Li イオンシナプス素子の動作メカニズムと実験結果を紹介する[5]. LiCoO<sub>2</sub> 膜厚の薄い TiO<sub>x</sub> が存在するカソード側に正電圧を印加すると, Li イオンがアノード側に移動して膜厚の厚い TiO<sub>x</sub> に入り込み, LiTiO<sub>x</sub> の低抵抗状態の膜となる. 下側は電気測定中の顕微鏡写真であり, Li イオンが移動して上部電極側に取り込まれて析出し, 逆方向の電圧を印加するとそれが元に戻る様子が繰り返し確認できる.

Fig.4 Li-based device for memristive characteristics. Upper: schematics for resistance change mechanism. Lower: the photos show the top electrode without and with Li ions from the bottom electrode.

Fig. 4 に素子の構造と動作原理の模式図を示 す. Li イオンが素子内部を移動し、電流が流れ る低抵抗状態 (LRS) と電流が流れない高抵抗 状態 (HRS) の間で所定の方向に変化する. 構 造は Ti などの電極と、正極すなわち正にバイア スしたときに Li<sup>+</sup>イオンを供給する Li イオン源 としての LiTiOx や LiCoO2/TiOx 金属酸化物複合 膜と、固体電解質としての LiPON などの Li イオン伝導層と、負極すなわち負にバイアスしたときに  $\text{Li}^{+}$  イオンを受け入れる  $\text{TiO}_{x}$  金属酸化物 層と Cu/Ti 電極とからなる. LiCoO2 は導電体で あるため、LiCoO2層のみの Li 濃度変調による 抵抗変化は不十分である. 基本的に TiOx は半導 体または絶縁体であるため  $TiO_x$  中の Li 濃度を 増減させることで,抵抗変化が生じるデバイス を設計できる、LiCoO<sub>2</sub>/TiO<sub>2</sub>の表面に垂直な方向 が Li イオンの移動方向である. Li イオンは, 正極と負極の間に電圧が印加されることで移 動する.

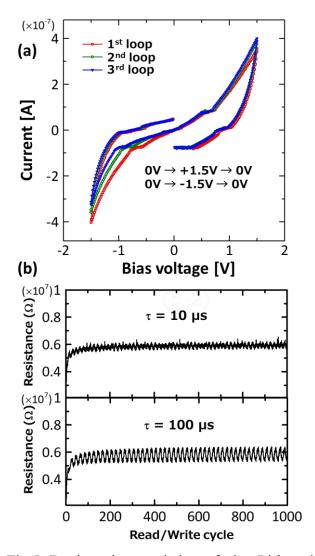

Fig.5 Device characteristics of the Li-based Memristive devices. (a) *I-V* curves and (b) repeated resistance measurements during read/write cycles.

Fig. 5 に作製した LiCoO<sub>2</sub>/TiO<sub>x</sub>/LiPON/TiO<sub>x</sub>/Cu の測定結果を示す. 電流は正バイアス, 負バイ アスともに徐々に増加するが、TiO<sub>x</sub>を添加した 試料では負バイアス時の電流が小さいことか ら, TiOxの抵抗変化が示唆され, バイアス電圧 に対してより対称な I-V 曲線が得られた (Fig.5(a)). なおこれとは対照的に、TiOx を含 まない試料は負バイアスで高い電流を示し 0.5V 付近でピーク電流を示すことから、電池評 価で良く観察される酸化還元反応の一種であ ることが示唆される. ある大きさの電流を流し た後にその電流を止めると, 残留電圧が発生す る. この LiCoO<sub>2</sub>/TiO<sub>x</sub>/LiPON/TiO<sub>x</sub>/Cu のデバイ スは、起電力は電池用途には十分ではないもの の全固体電池としても動作するといえる. 電流 パルス停止後の電圧は、内部デバイスの抵抗 R

を介してキャパシタンスCに蓄積された電荷が 放出されるため、指数関数的に低下する. -時間後, 残留電圧は 0.7V 程度に落ち着き, それ を維持した後、徐々に低下する. RとCが並列 で, 充電電圧 V すなわち起電力も直列の回路モ デルが描ける. 充電のための電流パルス時間が 短すぎる場合,また電流が小さい場合,残留電 圧は 0.7V 以下になる傾向がある. つまり多値 レベルの残留電圧を印加電流によって制御す ることができる[10]. Fig.5(b)では、パルス幅を  $10 \mu s$  と  $100 \mu s$  のそれぞれに固定し, 抵抗値が 増加する方向に変化させてそれをリセットす ることを繰り返し,抵抗の変化を調べた結果を 示す. この素子には短期・長期の可塑性がある ようで、パルスを繰り返すことで抵抗値が徐々 に活性化していく. パルス数ごとに抵抗値が分 離できれば分解能が得られていると判断して 結果的に 32 値のメモリ分解能が得られた. 得 られた2端子デバイスの多値抵抗変化は, までに報告されている Li イオンベースの 3 端 子デバイスに近いレベルである.このように実 証されたデバイスは、電解によってデバイス内 の Li イオンの分布を変化させ、LRS と HRS を 実現する新しいタイプの2端子メモリスティブ 素子と言える. 従来のメモリスタは、両端に TiO<sub>2</sub>などの金属電極を持つ構造であり、抵抗制 御の材料として電荷移動度の低い酸素欠損を 用いるため、LRS や HRS を安定に維持するこ とが困難であり、各素子の特性のばらつきや揺 らぎが大きくなる. これに対し, Li イオンは酸 素欠陥よりも移動度が大きいため電界による 移動が均一化され、各素子の抵抗値のばらつき が小さくなることも期待される. ばらつきや歩 留まりを高めていくことは積和演算用途では 重要である。

Fig.6 Reservoir computing with synapse devices at readout neurons for STDP learning.

また Fig. 6 に示すようなリザバーコンピューティング応用であれば、シナプス素子に求められる抵抗制御の精度が比較的低いためさらに応用が広がる可能性がある[5]. 今後さらなる用途開拓のためには素子構造や評価方法を検討し、メモリ分解能を向上させる必要があるものの、抵抗変化に電池効果を組み合わせた新しい動作原理の素子は、ニューロモルフィックに限らず新しい電子回路を創出する応用可能性を秘めている.

### 4. まとめ

本稿では、薄膜積層構造の金属酸化物メモリ スティブ素子を用いてアナログ抵抗変化をニ ューラルネットワーク回路に応用したニュー ロモルフィック技術を紹介した. 脳神経の可塑 性を模倣した Spike-Timing Dependent Plasticity (STDP) により抵抗を制御でき、自律型の学習 器の実現に向けて有望である. また新しい方向 性として, リチウム (Li) などイオンを用いて 素子の性質を可変にする技術を紹介した. 具体 例として, リチウムイオン二次電池の正極材料 として用いられる LiCoO<sub>2</sub> と固体電解質の薄膜 を組み合わせて、リチウムイオン伝導による抵 抗変化デバイスを紹介した. これら新規なニュ ーロモルフィック技術はリザバーコンピュー ティングなどで有用と見込まれ,将来の人工知 能 (AI) ハードウェアの高性能化に向けた応用 探索が今後も注目される.

#### References

[1] R. Berdan, T. Marukame, K. Ota, M. Yamaguchi, M. Saitoh, S. Fujii, J. Deguchi, Y. Nishi, Nature Electronics, Vol. 3, Issue 5, pp 259-266, 2020. [2] T. Marukame, Y. Nishi, S. Yasuda, T Tanamoto,

- Jpn. J. Appl. Phys., Vol. 57, Issue 4S, pp. 04FK06, 2018.

- [3] T. Marukame, J. Sugino, T. Kitamura, K. Takahashi, Y. Tamura, K. Nomura, K. Mizushima, Y. Nishi, Jpn. J. Appl. Phys., Vol. 59, Issue 4, pp. 040606, 2020.

- [4] Y. Nishi, K. Nomura, T. Marukame, K. Mizushima, Scientific Reports, Vol. 11, Issue 1, pp. 18282, 2021.

- [5] T. Marukame, K. Mizushima, K. Nomura, Y. Nishi, IEEE J. of the Electron Devices Society, pp. 602-610, 2023.

- [6] T. Marukame, K. Nomura, M. Matusmoto, S. Takaya, Y. Nishi, IEEE International Symposium on Circuits and Systems (ISCAS), pp. 1-5, Florence, Italy, 2018.

- [7] T. Marukame, J. Sugino, T. Kitamura, K. Ishikawa, K. Takahashi, Y. Tamura, R. Berdan, K. Nomura, Y. Nishi, IEEE International Symposium on Circuits and Systems (ISCAS), pp. 1-5, Sapporo, Japan, 2019.

- [8] T. Marukame, J. Sugino, T. Kitamura, K. Ishikawa, K. Takahashi, Y. Tamura, K. Nomura, K. Mizushima, Y. Nishi, IEEE International Symposium on Circuits and Systems (ISCAS), pp. 1-5, Virtual, 2020.

- [9] R. Berdan, T. Marukame, S. Kabuyanagi, K. Ota, M. Saitoh, S. Fujii, J. Deguchi, Y. Nishi, IEEE Symposium on VLSI Technology, pp. T22-T23, Kyoto, Japan, 2019.

- [10] K. Ota, M. Yamaguchi, R. Berdan, T. Marukame, Y. Nishi, K. Matsuo, K. Takahashi, Y. Kamiya, S. Miyano, J. Deguchi, S. Fujii, M. Saitoh, IEEE International Electron Devices Meeting (IEDM), pp. 6.2.1-6.2.4, San Francisco, USA, 2019.

- [11] T. Marukame, K. Mizushima, K. Nomura, J. Sugino, T. Kitamura, K. Takahashi, Y. Tamura, and Y. Nishi, SSDM2020.

# 二次元異種材料の接合技術と新機能創出

#### Functional devices based on van der Waals Junctions of 2D Materials

町田 友樹

東京大学 生産技術研究所 〒153-8505 東京都目黒区駒場 4-6-1 Tomoki Machida

Institute of Industrial Science, University of Tokyo, 4-6-1 Komaba, Tokyo 153-8505, Japan Tel:+ 81-3-5452-6742 (e-mail:tmachida@iis.u-tokyo.ac.jp)

#### **Abstract**

Recent advances in transfer techniques of atomic layers have enabled one to fabricate van der Waals junctions of various two-dimensional (2D) materials. Here, we present our recent experiments on (i) subband electronics based on multilayer transition metal dichalcogenides, (ii) control of inversion symmetry using van der Waals assembly of 2D materials, and (iii) 3D manipulation technique of 2D materials.

#### 1. はじめに

ファンデルワールス接合では、①界面において格子整合の制約がなく、②原子レベルで平坦な理想的界面が実現し、③構成要素となる二次元結晶の選択肢が極めて広い。さらに、④格子整合系ではあり得ない「原子層間の捻り角度」という設計自由度があり、バンド構造が制御できる。既存の材料系では得られない物性が発現する可能性があり、基礎・応用の両面で幅広い可能性を秘めている。

そして現在、同一または異なる二次元物質を 接合することにより、単体では全く考えられな かった性質が出現する例が明らかになりつつ ある。グラフェンとグラフェンを魔法角(≈1.1 度)と呼ばれる特定のツイスト角度で積層する ことで超伝導が発現するのが顕著な例である。 二次元物質同士の相互作用を積極的に使うこ とで、現在の三次元物質科学の限界を超えたブ レイクスルーをもたらす可能性がある。「二次 元物質の多様さ」×「ファンデルワールス集積 技術」の組み合わせにより無限の組み合わせの 構造が得られ、新たな学理創出の理想的な舞台 となる。本講演では特に複数層遷移金属ダイカ ルコゲナイドを利用したサブバンドエレクト ロニクスへの展開について議論する予定であ る。

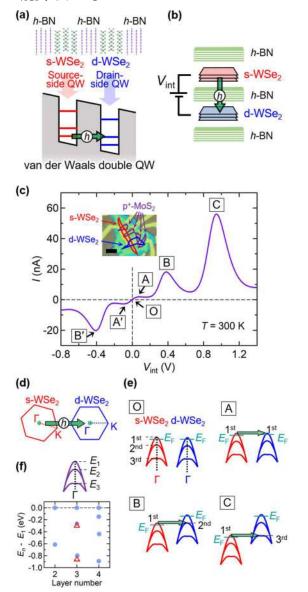

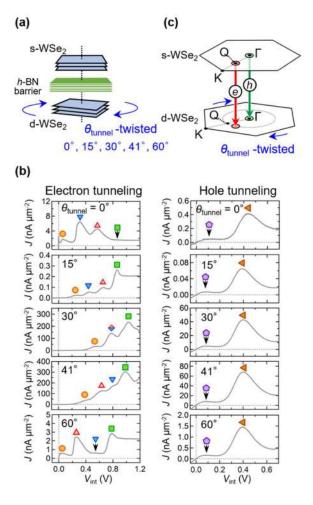

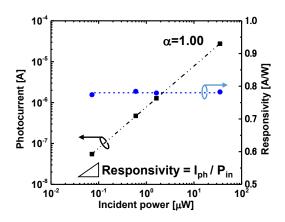

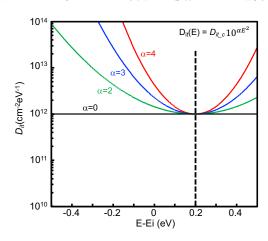

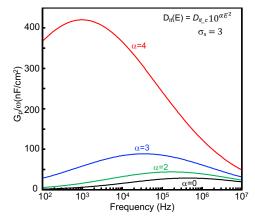

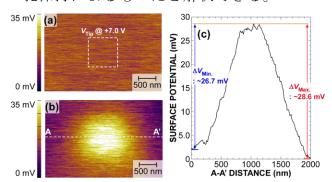

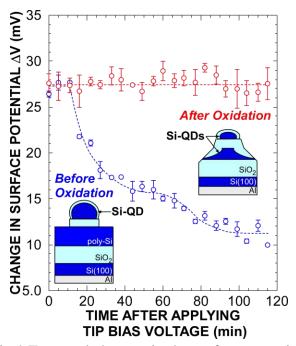

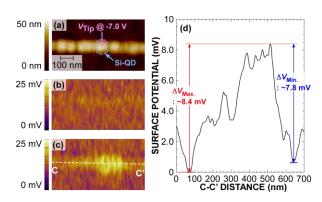

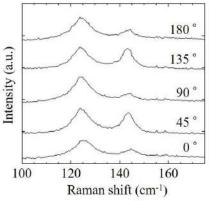

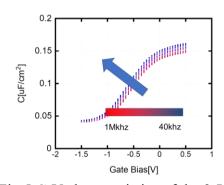

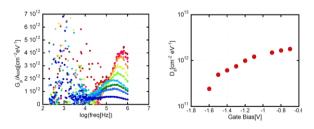

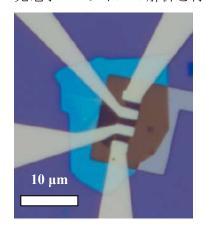

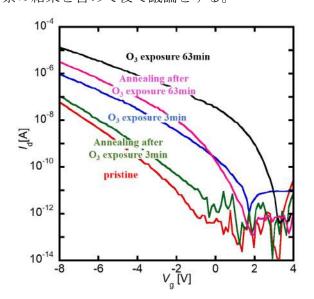

## 2. サブバンドエレクトロニクスへの展開

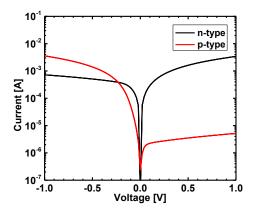

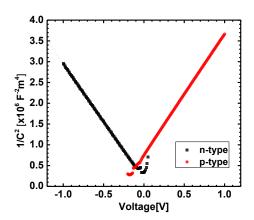

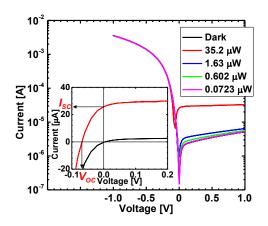

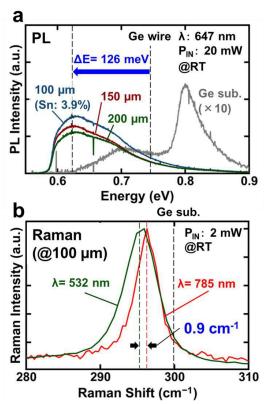

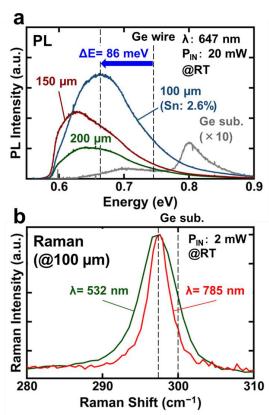

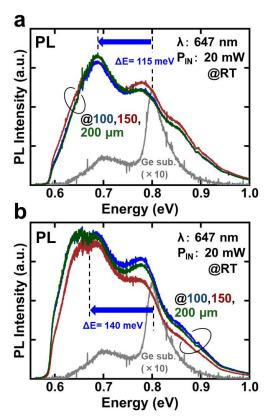

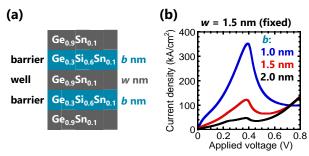

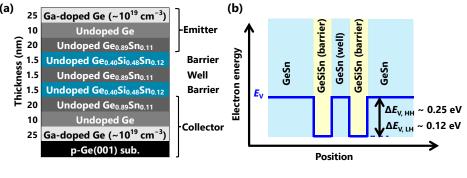

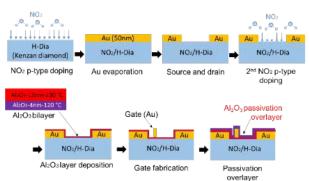

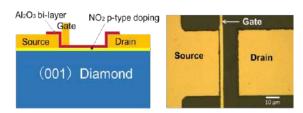

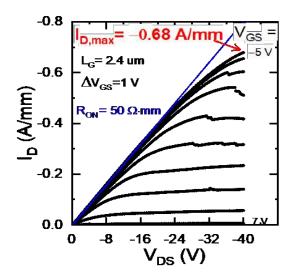

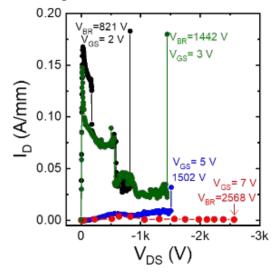

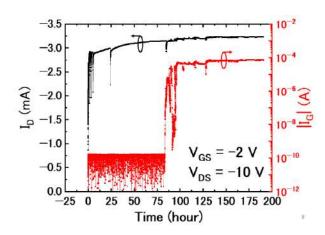

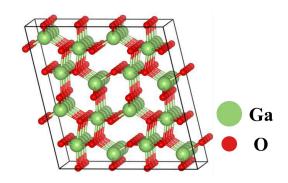

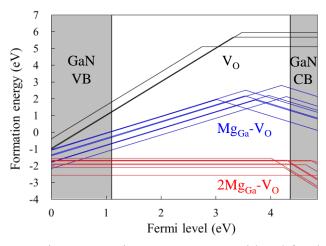

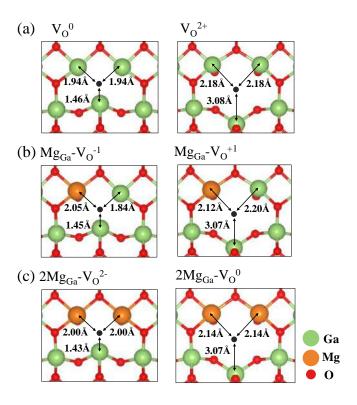

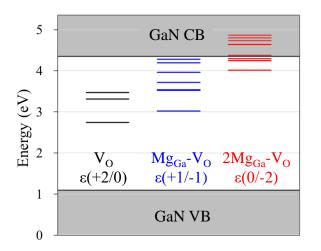

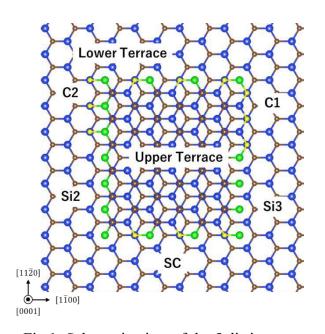

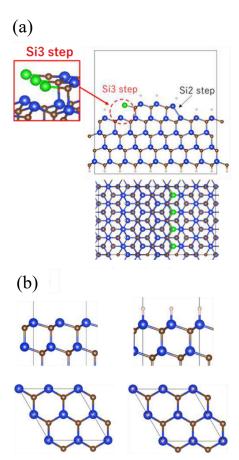

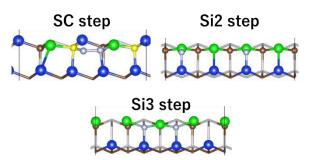

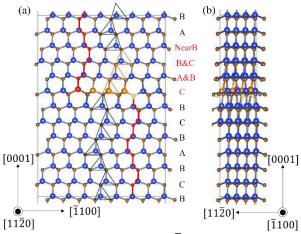

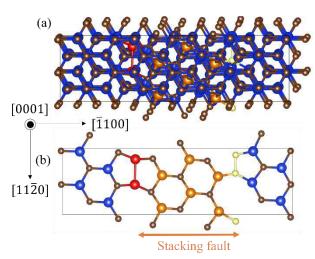

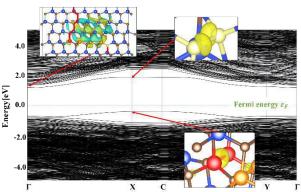

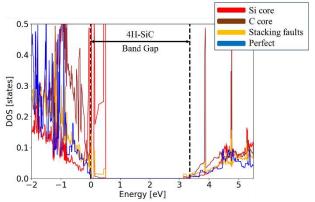

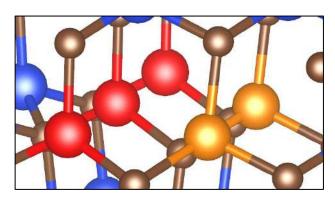

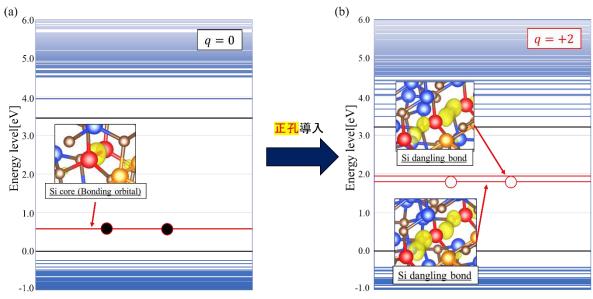

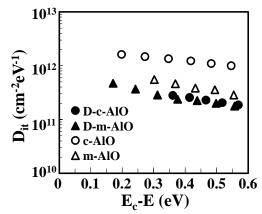

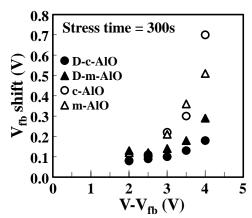

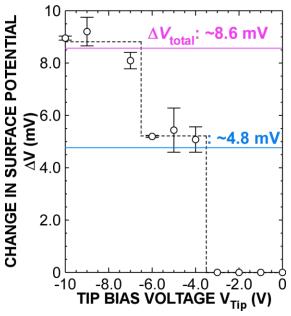

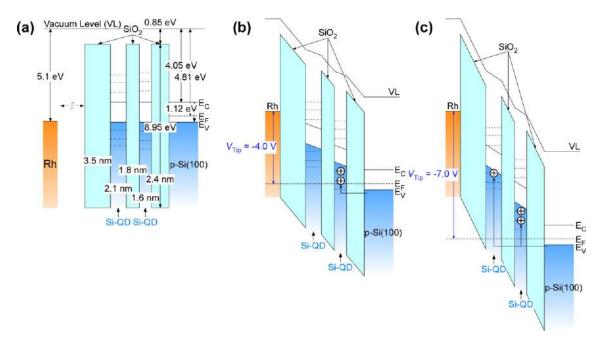

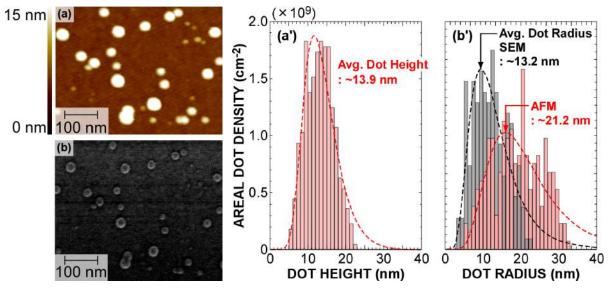

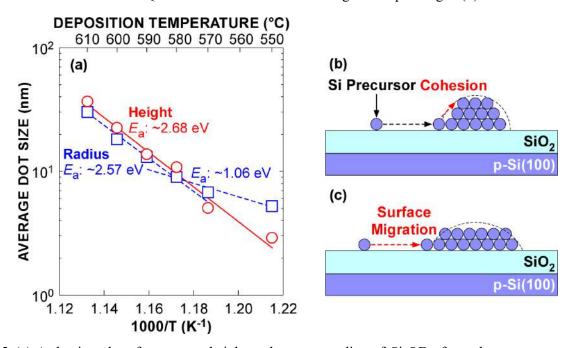

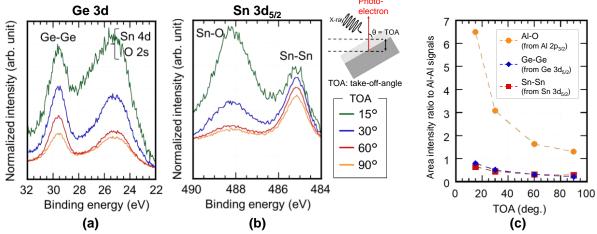

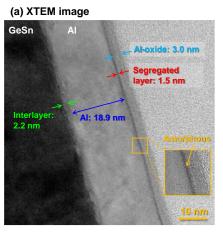

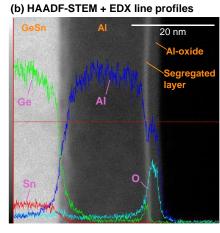

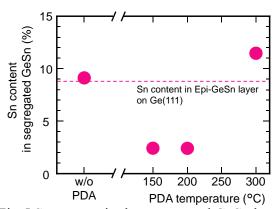

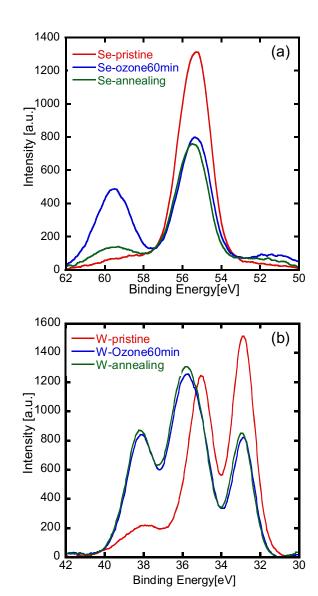

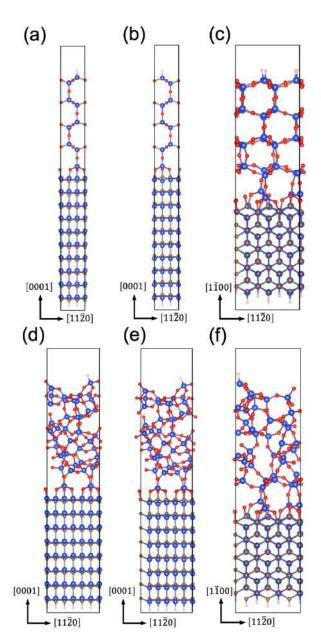

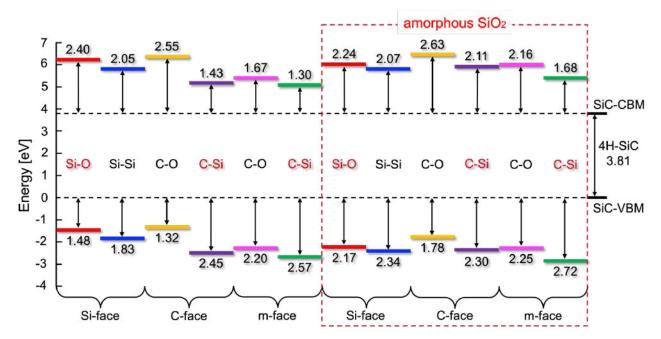

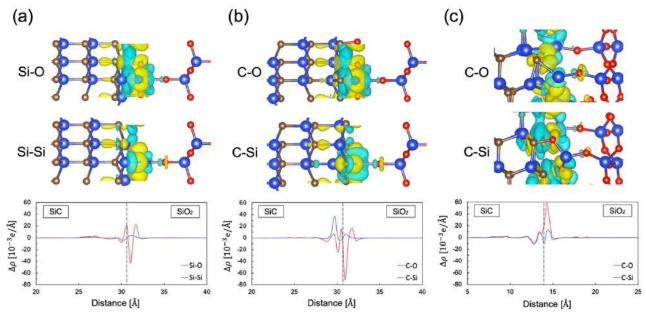

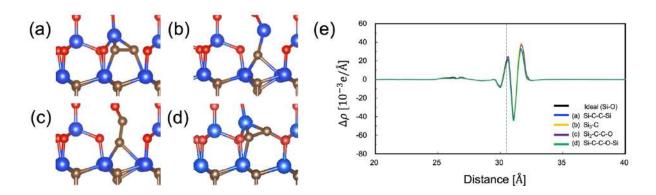

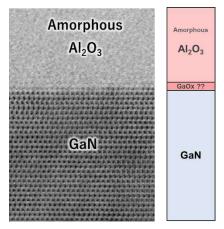

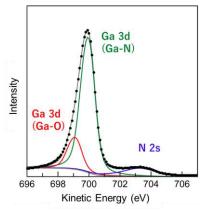

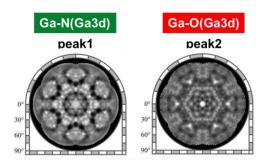

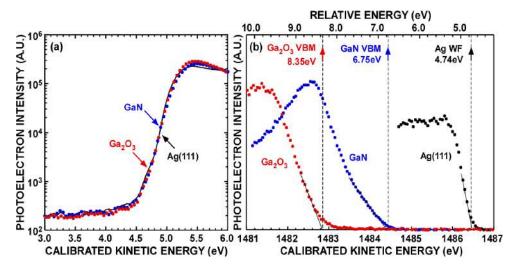

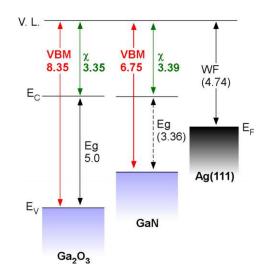

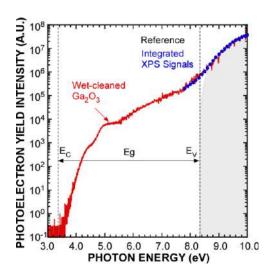

複数層の遷移金属ダイカルコゲナイドは間接遷移半導体であり、応用面で注目されることが少なかった。一方、サブバンドが形成されるため、自然発生的な量子井戸として振る舞い、サブバンドエレクトロニクスへの展開可能性を秘めている。